# **EPLD HANDBOOK**

Copyright © 1984, 1985 ALTERA Corporation.

## PATENT PENDING

The following are trademarks of Altera Corporation: EP300, EP310, EP600, EP900, EP1200, EP1210, EP1800, PLDS2, PLS2, PLCAD, PLE. ASAP is a trademark of Altera Corporation. TURBO-BIT is a trademark of Altera Corporation. PAL is a trademark of Monolithic Memories Inc. CROSSTALK is a trademark of Microstuf Inc. PC-CAPS is a trademark of Personal CAD Systems Inc. Dash-2 is a trademark of FutureNet Corporation. MS-DOS is a trademark of MicroSoft Corporation. WordStar is a trademark of MicroPro Corporation. ABEL is a trademark of Data I/O Corporation. CUPL is a trademark of Assisted Technology Inc. A+PLUS design elements and Mnemonics are Altera Corporation copyright. CHMOS is a trademark of Intel Corporation, IBM is a registered trademark of International Business Machines, Inc., A+PLUS, NetMap and LogicMap are trademarks of Altera Corporation. ALTERA does not assume any liability arising out of the application or use of any product described herein; neither does it convey any license under its patent rights nor the rights of others. ALTERA reserves the right to make changes at any time in order to improve reliability, function or design and to supply the best product possible.

ALTERA cannot assume any responsibility for any circuits shown or represent that they are free from patent infringement.

ALTERA CORPORATION 3525 MONROE STREET, SANTA CLARA, CA 95051 (408) 984-2800

# the Logical Alternative

# HOW TO USE THIS HANDBOOK

This handbook is organized in sections progressing from overview to detail. However, it is not necessary that it be used in this manner. If you are already familiar with Altera EPLDs and the associated design support versus other semicustom logic alternatives, you can go right to the product data in Section 2. On the other hand, if you're venturing into EPLDs or semicustom logic for the first time, you may choose to acquaint yourself with Section 1 which includes some brief history and a discussion of the technology issues and alternatives in the application specific market. Application information is contained in Section 3.

To place an order, go directly to the Appendices in Section 4 for ordering information, package outlines, or distributor locations.

If this Handbook doesn't answer your questions, please call on our toll-free numbers, 1-800-821-8124 (outside California) or 1-800-654-4236 (inside California), and we will help you directly.

| EPLD: Erasable Programmable Logic Device | s Page 5   |  |

|------------------------------------------|------------|--|

| - INTRODUCTION TO ALTERA                 |            |  |

| ■ INTRODUCTION TO ALTERA                 | 7          |  |

| ■ THE EPLD CONCEPT                       | 8          |  |

| ■ CMOS EPROM TECHNOLOGY                  | 10         |  |

| ■ DEVELOPMENT SYSTEMS & SOFTWARE         | SUPPORT 12 |  |

| DATA SHEETS                              | Page 17    |  |

|                                          |            |  |

| ■ PRODUCT LIST                           | 18         |  |

| ■ SELECTION GUIDE                        | 19         |  |

| ■ DATA SHEETS                            | 20         |  |

| APPLICATION INFORMATION                  | Page 83    |  |

| - APPLICATION MOTES                      | 24         |  |

| ■ APPLICATION NOTES                      | 84         |  |

| ■ APPLICATION BRIEFS                     | 148        |  |

| APPENDICES                               | Page 227   |  |

|                                          |            |  |

| ■ GLOSSARY                               | 229        |  |

| ■ TECHNICAL REFERENCES                   | 233        |  |

| ■ PRODUCT COMPATIBLITY                   | 233        |  |

| ■ PROGRAM SUPPORT                        | 234        |  |

| ORDERING INFORMATION                     | 235        |  |

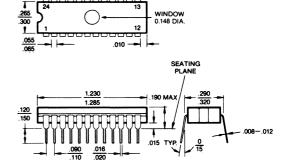

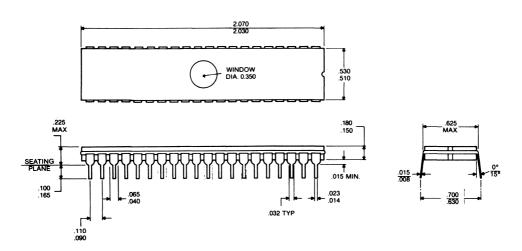

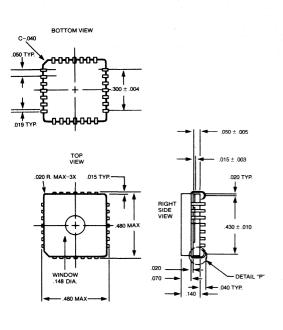

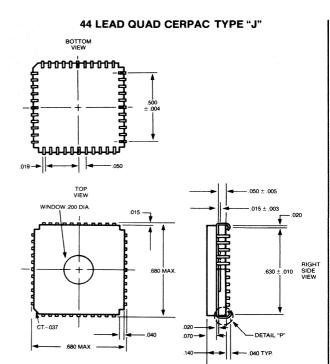

| ■ PACKAGING INFORMATION                  | 236        |  |

| ■ QUALITY INFORMATION                    | 238        |  |

|                                          |            |  |

| ■ ALTERA DISTRIBUTORS                    | 241        |  |

# Introduction to Altera

# **ALTERA CORPORATION**

# **BACKGROUND**

Altera was founded in June of 1983 on the premise that the broad based market of semiconductor logic users needed a new alternative for large scale custom logic. The founders of Altera believed that the problems of development cost, lead time, and flexibility associated with traditional vendor mask-customized solutions could be solved through the use of programmable standard components. This has led to the development and marketing of Altera's family of CMOS EPLD products. By combining CMOS and erasable technology with advanced design tools, Altera's EPLDs are targeted to replace TTL/74HC/CMOS 4000 random logic and low density gate arrays, reducing system cost, product size, and power requirements.

# **PRODUCT LINES**

Altera products fall into three groups:

- 1. Erasable Programmable Logic Devices(EPLDs)

- 2. Programmable Logic Development Systems

- 3. Software Development Support Tools

# **EPLD COMPONENTS**

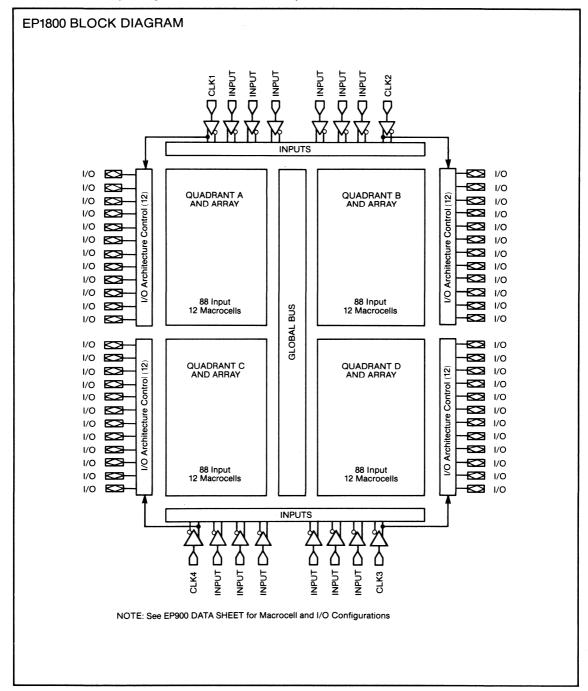

The EPLD family of components includes five initial devices that range in density from 300 to 1800 gates and with performance from 25 to 90 ns. All use low power CHMOS erasable technology and include between 8 and 48 flipflops. EPLDs have general system applicability by allowing the replacement of many low density logic functions with single packages. This saves physical space while at the same time reduces power requirements and system failure rates.

# **DEVELOPMENT SYSTEMS**

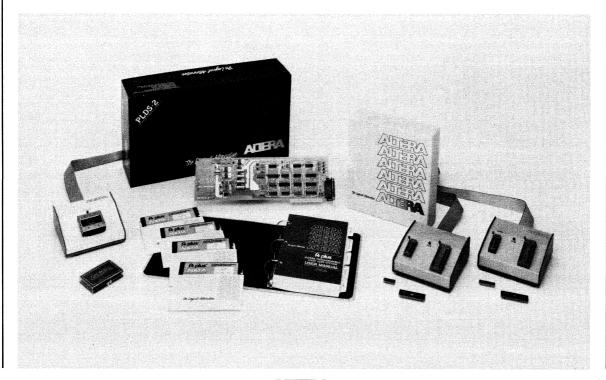

Altera Development System products are self contained IBM PC compatible development systems for designing with and programming Altera EPLD components. Each development system contains everything the first time user needs to make an IBM PC (or compatible) be a logic development system. Each system comes with programming hardware, fully documented software, and sample devices to allow the new user to design quickly and easily.

# **SOFTWARE SUPPORT TOOLS**

Software support tool products include A+PLUS (Altera's proprietary automatic logic compiler), schematic symbol libraries, a logic simulator, interfaced schematic capture packages from Future Net and P-CAD (Altera is a value-added remarketer) and other development tools. This group of support tools is a growing family of products designed to make the designer's task quicker and easier to perform.

Altera's products are sold by manufacturers representatives and major electronic distributors throughout the world. Intel Corporation is a second source for many of the Altera products.

# PHILOSOPHY AND DIRECTION

Altera believes that advanced development tools are a critical factor for the advancement of programmable semiconductor technology. In order that component utility and ultimately designer efficiency be maximized, the semiconductor and the software must be developed in parallel and concert. If one is subordinated to the other, the total product combination will suffer in performance and utility. In line with this belief, Altera has invested in approximately equal sized R&D staffs in the areas of Software Development and Integrated Circuit Design.

One clear benefit of this philosophy to the user is that of immediate support for new products. When Altera introduces a new product to the market place,

there will always be software and hardware support in place the day of introduction. This level of support and service is unique in the industry and is an integral part of Altera's philosophy.

Altera, as a Company, is focused entirely on the application of CMOS erasable technology to the user programmable logic market. Altera's goal is to serve its customers with superior quality in both products and services. By focusing exclusively on this market area, Altera expects to be able to provide a higher level of technical support as well as demonstrate a greater rate of technical innovation. It is the Company's intent to be recognized as the technology and market leader in this product area.

# The EPLD Concept

# THE EPLD CONCEPT

Logic is the key proprietary ingredient in electronic system design. The ability to rapidly complete the logic engineering of a system, and quickly and cost effectively bring the product to market, is critical. This can be a deciding factor in the ultimate success or failure of a product and a company. To achieve performance in the marketplace, more and more manufacturers have sought higher levels of integration (functional density) for the electronic components in their products. This has led to various forms of custom chips that require lengthy development lead times and sizable design costs. The concept of EPLDs is to provide the benefits of large scale integration without the drawbacks of custom chips.

# **WHY INTEGRATE?**

The benefits of large scale integration are becoming more widely known. A few of the most significant benefits are:

LOWER MANUFACTURING COSTS: The use of customized LSI circuits instead of standard SSI/MSI (small and medium scale) components reduces required printed circuit board space, thereby significantly reducing board costs. Through integration, savings can also be realized in the individual costs of the passive components, reduced assembly and inventory costs.

**LOWER POWER:** In this age of need for energy efficiency, integration can reduce the power consumption of systems by orders of magnitude. Additional benefits are less expensive power supplies and elimination of cooling fans.

HIGHER RELIABILITY: LSI circuits have been shown to have statistically higher reliability than equivalent systems comprised of many low density standard components. When an LSI circuit implementation is replacing electro-mechanical functions, system lifetimes will be greatly extended since there are no moving parts to wear out. Required maintenance is lower and system reliability is higher.

### PROPRIETARY DESIGN PROTECTION:

An LSI circuit design solution creates barriers to market entry for competitors. It makes "reverse engineering" of your design significantly more difficult for potential imitators.

**ADDITIONAL FEATURES:** At the same time the benefits of the previous items are occurring, LSI circuit implementation often allows the incorporation of optional and special features at a very low incremental cost.

# **ALTERNATIVES FOR ACHIEVING**

# LARGE SCALE LOGIC INTEGRATION

As end users of semiconductors were compelled to move to higher and higher levels of integration for the reasons just discussed, chip designers found it increasingly difficult to define larger and larger common "building blocks" of logic. These difficulties led to the emergence of the *user-defined* Application-Specific Integrated Circuit (ASIC). Over the past five years, this has been one of the fastest growing segments of the semiconductor business, indicating increasing use of customized LSI in end products.

The options presently available for applicationspecific logic are:

> Full Custom Standard Cell Library Gate Array User Programmable

Each of these options will be briefly described along with the benefits and tradeoffs.

**FULL CUSTOM:** The full custom alternative supplies the highest efficiency in chip area and performance. These circuits, typically handcrafted, can be tailored to give the best functional performance with the highest level of integration, the smallest silicon area, use the lowest power, and be produced for the least cost at high production volumes.

Offsetting these optimal characteristics, however, are long development lead times (long time to market: 1 to 3 years), and large development costs (\$50,000-\$250,000). These drawbacks have led to the popularity of Standard Cell Library and Gate Array custom semiconductors.

**STANDARD CELL LIBRARY:** The standard cell library approach represents an integrated circuit which is composed of predesigned and precharacterized cells chosen from a computer "data base" library of cells. A specific function is realized by choosing, placing, and interconnecting these cells.

Some of the specific advantages and disadvantages of a standard cell library approach are as follows. Advantages are high integration capability with gate densities up to 20,000 gates; medium design time (3-6 months); and low production cost when produced in significant volumes. Some of the disadvantages of cell libraries are that all mask layers are customized; the technology is the highest cost form of semicustom design, and results in a non-standardized pin out, requiring unique packaging, bonding, and test hardware for each circuit. Also, no second sourcing is presently available, and the process technology typically lags the state-of-the-art due to library maintenance and characterization required for each wafer fabrication process upgrade.

**GATE ARRAYS:** Gate arrays are integrated circuits that contain a regular, usually square, matrix of predefined logic gates. Custom functions are realized by means of a unique customized interconnection of the gates and the input and output structures. The custom interconnection varies from one layer metal to three layer metal, with a multitude of techniques used to design the connections.

The advantages of gate arrays are that they are simpler and cheaper to design than full custom or cell library circuits, and can be produced with less lead time. The development costs and lead times remain significant, however.

A comparison of these mask customized alternatives is shown below:

| ALTERNATIVE   | % OF WAFER<br>PRE-PROCESSED | DEVELOPMENT<br>COST/CHIP<br>(K-\$) | PROTOTYPE<br>LEADTIME<br>(MONTHS) |

|---------------|-----------------------------|------------------------------------|-----------------------------------|

| FULL CUSTOM   | 0%                          | \$50-250                           | 9-18                              |

| STANDARD CELL | 0%                          | \$30-90                            | 3-6                               |

| GATE ARRAY    | 80-90%                      | \$10-40                            | 11/2-5                            |

|               |                             |                                    |                                   |

None of these three mask customized solutions have been wholly satisfactory for system designers and manufacturers due to several problems:

Development lead times are relatively long, requiring from 6 to 20 weeks for the fastest solution.

Design costs are significant, varying from \$10K to \$40K as a minimum.

Inventory is dedicated which is expensive and prohibits adequate second sourcing.

Semiconductor distributors have difficulty participating in this business — thus limiting widespread use.

None of the solutions mentioned address the fundamental issue that engineering is inherently an interactive process. Design changes in midstream are not allowed due to lead time and inventory constraints.

As a result of these restrictions, many designers are still reluctant to switch from TTL standard logic to application-specific logic.

USER PROGRAMMABLE LOGIC: Attempts to eliminate these restrictions have led to an increasing interest in programmable logic devices. The concept of user programmable logic is to provide the designer with the benefits of custom LSI chips from standard products. The benefits of such parts include off-the-shelf availability, minimal design costs, multiple sourcing from distributors and manufacturers, and flexible interchangeable inventory.

# **BIPOLAR FUSE TECHNOLOGY**

In the past all programmable logic products were implemented using bipolar fuse technology. These products eliminated the lead time and development cost penalties of the mask customized solutions previously mentioned, but brought with them their own inherent limitations:

Bipolar, with its high power dissipation, cannot provide the integration density required.

Fuse programming does not allow complete testing at the factory and is inefficient in silicon utilization.

The devices can only be programmed once; therefore, mistakes in development result in scrap, a significant penalty with high density parts.

The programming software and development tools are primitive and tedious to use.

# **CMOS ERASABLE TECHNOLOGY**

Altera was the first supplier to overcome the problems of programmable logic when it introduced its EPLD line of user-programmable logic devices incorporating CMOS floating-gate technology.

Altera EPLDs are manufactured with high-speed complementary metal oxide semiconductor (CHMOS\*) technology. Compared to bipolar fuse technology, CMOS provides lower power dissipation and a cooler operating temperature which enables designers to pack a greater number of logic functions onto a chip. The EPLD family, introduced in July 1984, provides low power consumption, integration densities from 300 to 1800 gates, and full testability.

Altera's EPLDs use an EPROM programming mechanism. This technology, used in MOS memories since the early 1970's, brings further advantages. It enables the devices to be reprogrammed in the event of any design changes. The fact that programming can be erased permits thorough testing during the manufacturing process and flexibility in the hands of the user. Overall, it puts a much greater degree of control in the hands of the system designer.

EPLDs resolve the earlier limitations of userprogrammable logic and the limitations of mask customized logic. Large scale custom logic can now be created without a long development cycle or significant cost of design. Minor design changes or adjustments can be made quickly and efficiently without inventory jeopardy. These conclusions are demonstrated in the comparison below.

| ALTERNATIVE                                | % OF WAFER<br>PRE-PROCESSED | DEVELOPMENT<br>COST/CHIP<br>(K-\$) | PROTOTYPE<br>LEADTIME<br>(MONTHS) |

|--------------------------------------------|-----------------------------|------------------------------------|-----------------------------------|

| FULL CUSTOM<br>STANDARD CELL<br>GATE ARRAY | 0%<br>0%<br>80-90%          | \$50-250<br>\$30-90<br>\$10-40     | 9-18<br>3-6<br>1½-5               |

| USER<br>PROGRAMMABLE<br>EPLDs              | 100%                        | 0                                  | OFF THE<br>SHELF                  |

# **EASY TO USE**

For user-programmable circuits to reach the broad base of existing SSI/MSI TTL users, the programming and design tools must meet three criteria: (1) be low cost, (2) easy to learn and use, and (3) have personal availability and access. Today, the most widely available source of computing power is the personal computer. By creating development tools that fit the personal computer environment, all three of these criteria can be met.

# **SUMMARY**

Altera, with its ELPD products and development system support tools, has addressed the limitations of gate arrays and fuse programmable logic. The benefits to the system designer are:

- no lead times

- · low design costs

- multiple sourcing from distributors and manufacturers

- · ease of design changes

- multiple programming, if necessary

- low power dissipation from CMOS technology

- high density products that maximize function, integration, and quality

- maximum flexibility in each chip, that comes from programmable architecture, and the ability to erase and reprogram

- a self contained low-cost sophisticated development system.

EPLDs are now a cost-effective solution to the problem of large scale logic integration. EPLDs are the simplest form of high density application-specific logic to implement. As such, they will be a key ingredient to boosting electronic engineering productivity over the next decade.

# CMOS EPROM Technology

# **CMOS EPROM TECHNOLOGY**

To achieve the goals established for EPLD products, Altera performed a thorough evaluation of semiconductor technology. This resulted in the selection of CMOS and floating gate (EPROM) technologies. CMOS was chosen for its density, reliability, testability, and low power. Each of these technologies are described in more detail below.

# **WHAT IS CMOS?**

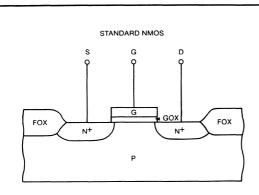

Complementary metal oxide semiconductor (CMOS) technology simply involves the fabrication of n and p channel MOS transistors on the same substrate and is analogous to using both npn and pnp transistors in a bipolar circuit. CMOS typically uses only enhancement-mode transistors, in contrast to NMOS which may employ both enhancement and depletion device types.

## **LOW POWER**

The use of enhancement-only device types give CMOS its automatic power-down capability since use of both n and p channel MOSFETs in the basic inverter gate means one of the transistors is always off. Thus, there is no current path from power supply to ground and both active pull up and pull down paths exist for the load. This first feature gives CMOS its extremely low power dissipation in the standby mode (only leakage current flow), and the second means that CMOS devices can be very fast — faster than NMOS. (CMOS rise and fall times are short and symetrical, while NMOS has a short fall time but a significantly longer rise time because of its high resistance load, dictated by D.C. pull up/pull down considerations.)

# **NOISE IMMUNITY**

The simplicity of the inverter configuration and the transistor structure gives CMOS a wide margin of power supply. One outcome of the resulting increased logic swing is that it gives the technology excellent noise immunity — typically 45% of V<sub>CC</sub>, which is better than that of either TTL or NMOS.

# RELIABILITY

CMOS device junctions average about 20°C cooler than their NMOS counterparts. This gives CMOS up to more than 10 times the reliability edge with respect to failure rate. Additionally, high temperature operation (greater than 150°C) is possible with CMOS for short times because of this.

Altera manufactures its EPLDs using CHMOS\* n-well technology. This high speed CMOS technology provides lower power dissipation and a cooler operating temperature, enabling designers to pack a greater number of logic functions onto a chip. Altera's EPLDs use an EPROM-type programming mechanism. This technology, used in MOS memories since the mid-1970's, brings further advantages.

# **EPROM (FLOATING GATE TECHNOLOGY)**

Altera uses EPROM transistors in its EPLDs to perform all of the various customizing functions. By using the EPROM transistors as switches throughout the circuits, both architecture and individual connections can be configured.

# **HOW EPROMs WORK**

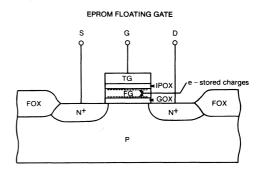

The EPROM transistor is built with the same structure as a standard NMOS silicon gate transistor, with the addition of a second polysilicon gate electrode that is electrically isolated from all other elements of the circuit by means of oxide regions which surround it on all sides.

In the unprogrammed state the floating gate is uncharged and does not influence transistor action. The transistor acts like a normal transistor whose gate oxide thickness is the sum of the thicknesses of the gate

oxide and the interpoly oxide. In this condition, the transistor is turned on if VCC is applied to the gate electrode.

To program the transistor, high voltages are applied to the gate and drain electrodes. This turns the transistor on very hard, with the result that energetic electrons are able to surmount the potential barrier and move through the gate oxide to the floating gate. There they accumulate until the effect saturates. Upon removal of the applied voltages, there is a net negative change left on the floating gate.

The effect of the stored charge is to increase the threshold (turn-on voltage of the transistor), such that when V<sub>CC</sub> is applied to the gate, the transistor remains off. This charge is very stable and under normal operating conditions it will not dissipate for many years.

# ADVANTAGES FOR LOGIC USERS

The advantages that CMOS and EPROM give the user of EPLDs are numerous. For instance, the lower power consumption makes battery and non-cooled applications possible. It also allows the production of higher density logic devices since the devices do not reach power dissipation limits. EPROM transistors, as well as being programmable, are also erasable. This permits users to re-use and re-program devices ultimately saving money. The erasibility saves in other ways too: because Altera can program all transistors and test them fully before shipment, 100% programming yield is assured to users. This was previously unknown with bipolar devices. Finally, EPLDs are secure. The logic that is programmed cannot be seen even if the chip is opened since the stored charges are invisible and captured on a buried layer of polysilicon. These are just some of the advantages that EPLDs offer by using the combination of CMOS and EPROM floating gate technologies.

TG = TOP POLY-SILICON GATE

IPOX = INTER-POLY OXIDE

FG = FLOATING POLY-SILICON GATE

GOX = GATE OXIDE

FOX = ISOLATION (FIELD) OXIDE

$N^+ = N^+$  SOURCE AND DRAIN

P = P-TYPE SUBSTRATE

S = SOURCE

G = GATE D = DRAIN

# Development Systems and Software Support

# INTRODUCTION

Programmable Logic Devices (PLDs) have seen a rapid, even dramatic rise in their market over the past few years. This has been due to a combination of factors acting favorably together: availability of a greater variety of devices, improved support tools, multiple sources, and increased design sophistication in the marketplace. The net result has been the emergence of a new technology which will see universal application over the next few years.

The bulk of this phenomenal growth has been in Field Programmable Logic Devices (FPLDs). Programmable by the user via a variety of technologies, instant turnaround has proven an invaluable aid in reducing time to market for the end-user.

Occupying an expanding niche between traditional TTL and LSI, FPLD capabilities have increased as older device families have been refined and new device concepts have been introduced. Lower power, higher performance, more flexibility are being built into new devices. The system designer, receptive to and educated in the use of such devices, reaps these benefits.

The challenge for those developing FPLD support tools and systems is to simplify the education process and provide an efficient translation of abstract design ideas into device programs. With the increased complexity of FPLDs, the user requires assistance at all stages of the design process from design conception through to test generation. Simple coding assemblers are no longer enough in the FPLD arena just as they have fallen out of favor for the bulk of microprocessor programming applications. As FPLDs push into the domain previously reserved for LSI and large-scale gate arrays, the demand for higher-level support tools, both hardware and software, will increase. Given the complexity of the design process and the proliferation of devices and features available, this is no small task.

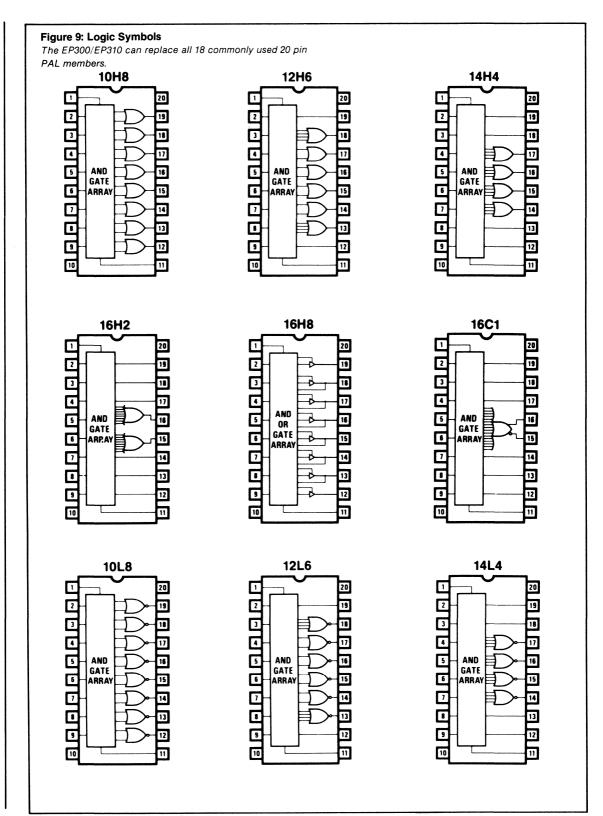

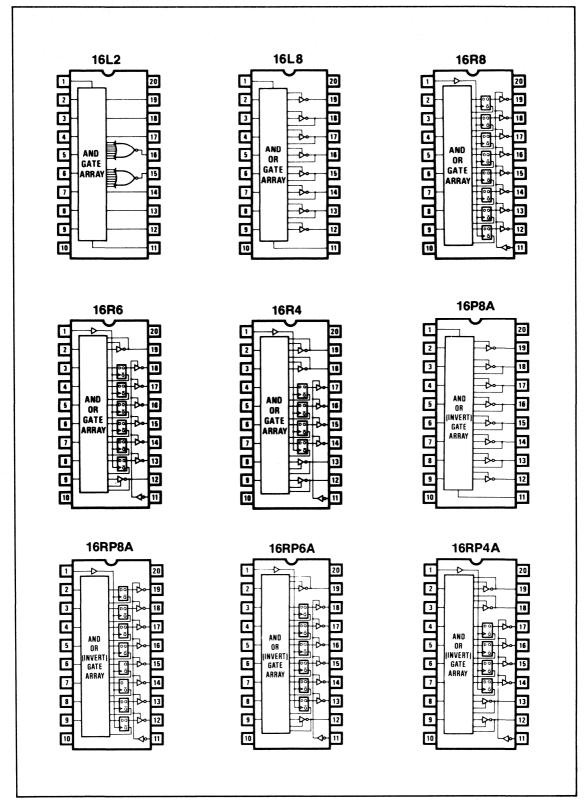

EPLDs (Erasable Programmable Logic Devices) emerged on the scene in 1984 with the introduction of Altera's EP300 component. Utilizing CMOS EPROM technology to retain programming information and a flexible Macrocell architecture allows one device to replace all members of earlier 20 pin PAL families. Low

CMOS power is an additional attraction for designers, as well as the reprogrammable nature of the EPROM technology.

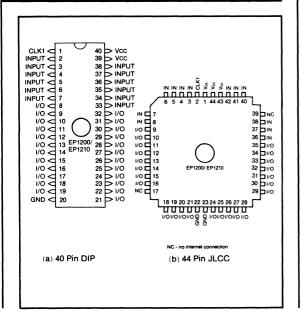

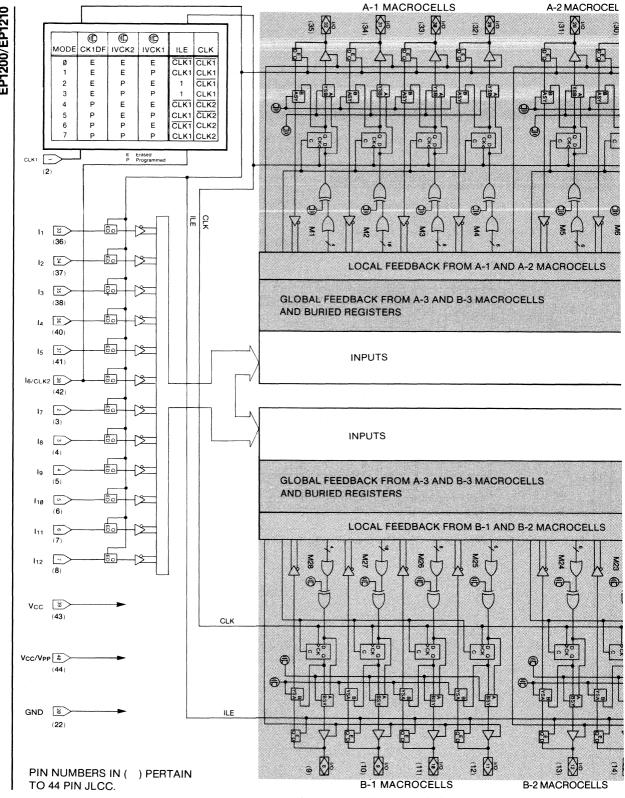

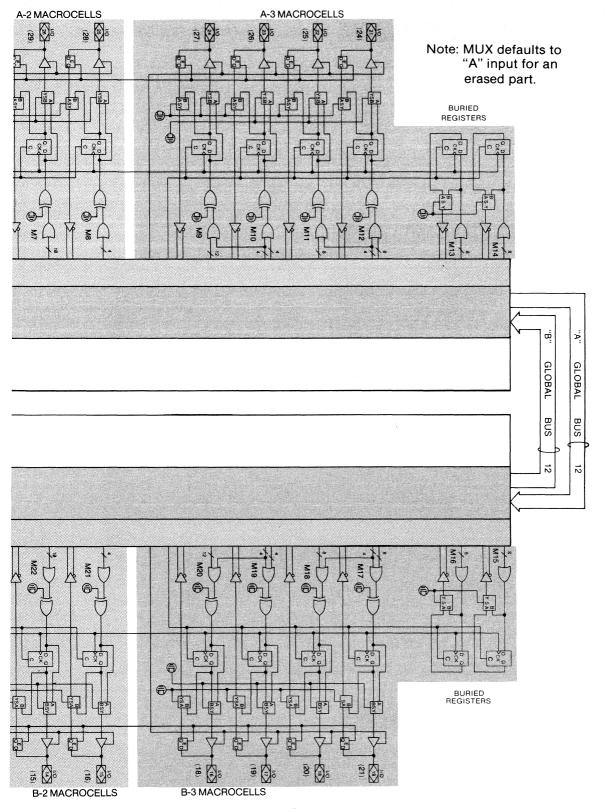

Soon after, Altera introduced the EP1200/EP1210 equipped with 28 flip-flops. The EP1200/EP1210 represented an integration level and speed-power product unmatched in previous devices. With the EP1200/EP1210, EPLDs were no longer considered just another PAL technology but a true contender for large-scale applications previously reserved for gate arrays.

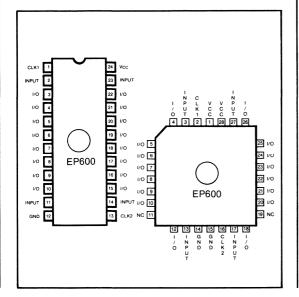

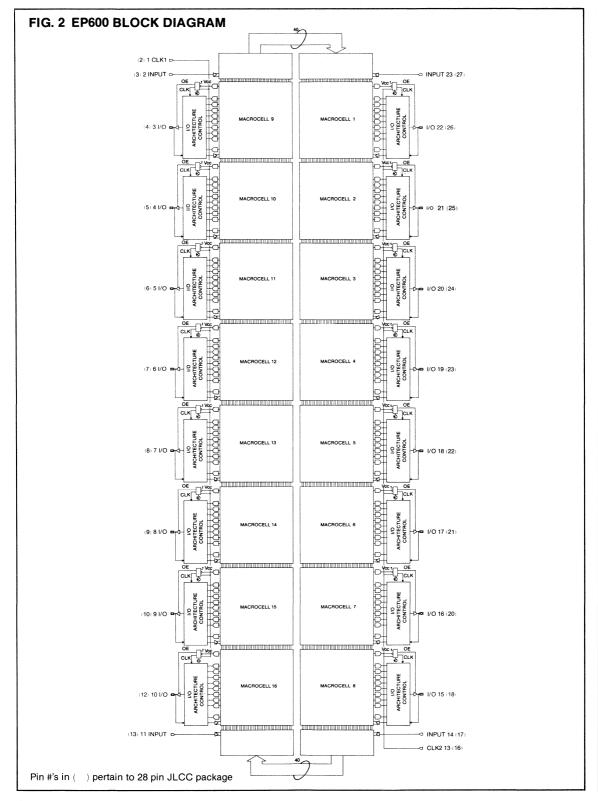

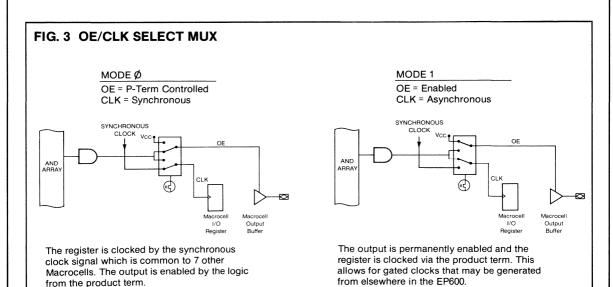

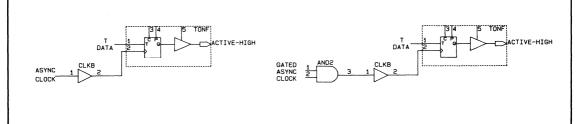

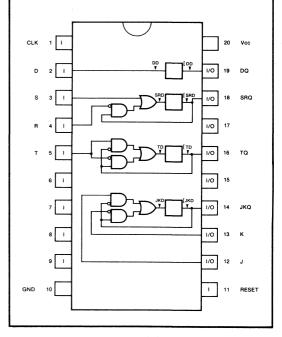

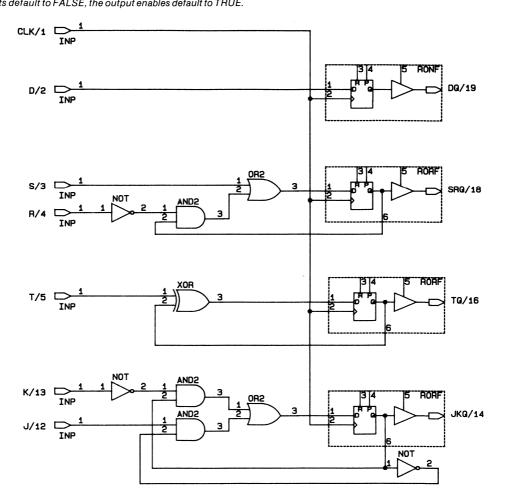

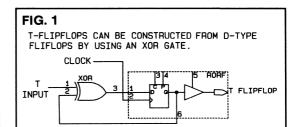

Altera's EP600 device with 16 macrocells, programmable flip-flop (D/T/JK/SR) types, and asynchronous or synchronous clocking of each flip-flop has enabled the system designer to implement a variety of random logic and flip-flops all on a single chip. The "Programmable" part of EPLD now designates not only the combinatorial logic portion, but the sequential (storage) element portion also, as well as the logic's clocking scheme! The breadth of applications for these devices thus expands dramatically.

Subsequent devices have already and will continue to build on these trend-setting concepts. Altera is committed to be the industry leader in innovation and being sensitive to customer needs.

This range of capability represents an expanding design support problem, however. Each device, while having basic features in common, has its own special design requirements in terms of design tools. Solving these specific problems in the context of the user's overall design needs is the key.

# FORCES DRIVING EPLD SUPPORT

The evolution of support tools for EPLDs has been driven by many factors, both direct and indirect. The goal has always been to allow the system designer to more efficiently turn his design concept into a programmed device, transforming his idea into silicon. As the efficiency of this process increases, the technology is more widely accepted.

Indirectly, EPLD support has experienced and benefitted from the general improvements in both design methodology and CAD/CAE technology (both hardware and software) enjoyed by the design world at large. EPLDs fit well into a structured design methodology given their regular, array based architectures. Their primitive elements map well onto established TTL primitives. As such, they have been able to exploit many of the common tools developed.

Evolution of device complexity and capability required a like improvement in supporting tools. Coding a bipolar PROM via a specification of 0's and 1's may be adequate, but to effectively design with and program a complex device such as Altera's EP1200/EP1210 requires a much more global view of overall design considerations. Schematic capture or other high-level descriptions of logic are then required to efficiently deal with this level of design complexity. Simple means to

implement device simulation and programming are also essential.

# INTRODUCTION TO A+PLUS SOFTWARE

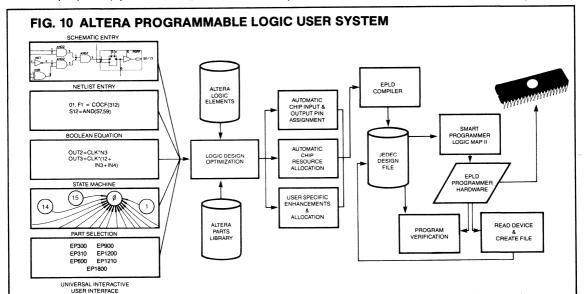

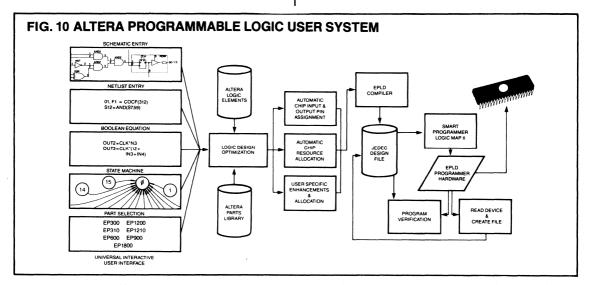

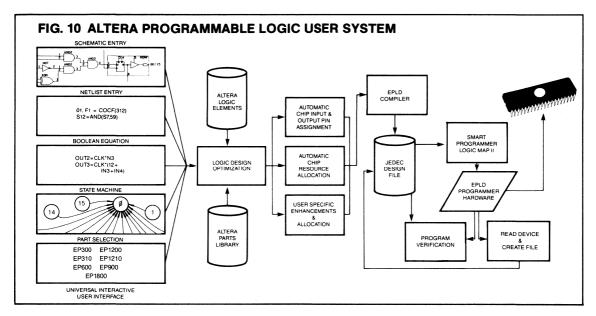

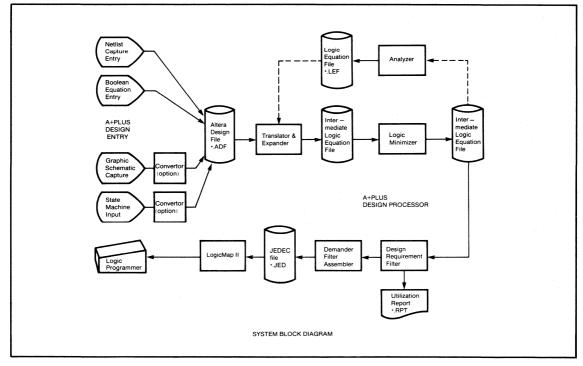

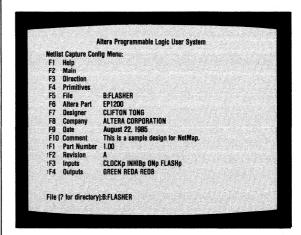

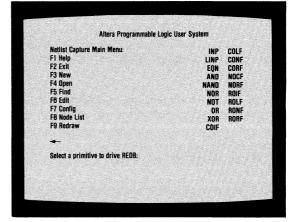

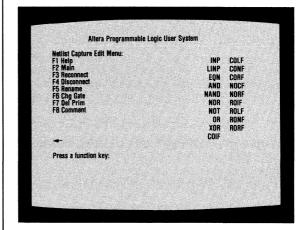

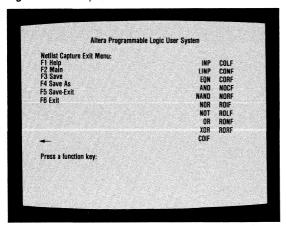

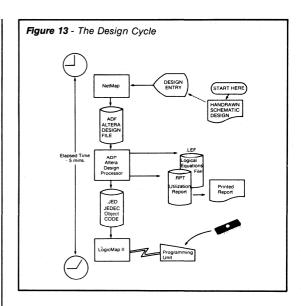

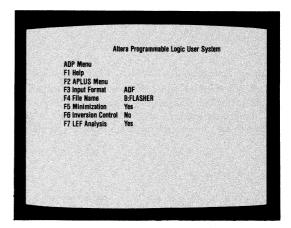

As in the area of component architecture, Altera is committed to provide effective, flexible solutions to the CAD/CAE problems the system designer faces. Particularly in those areas which require extensive device-specific knowledge, Altera has developed an effective set of PC-based CAD tools to handle the problems of design entry and programming. This package, known as A+PLUS (Altera Programmable Logic User System) provides a powerful design support tool that matches the continually expanding capabilities of Altera programmable logic devices.

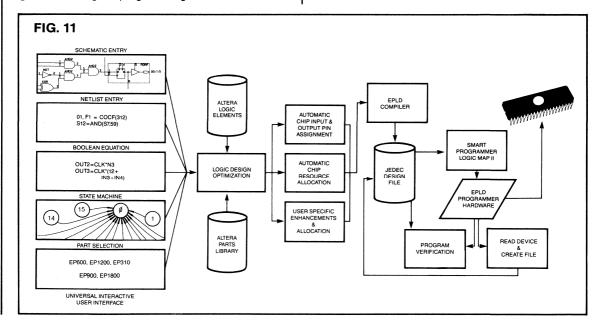

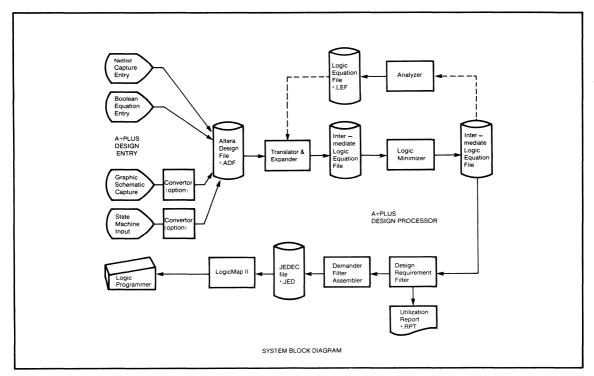

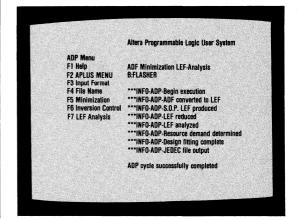

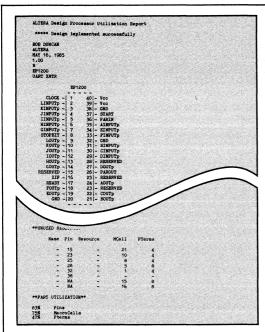

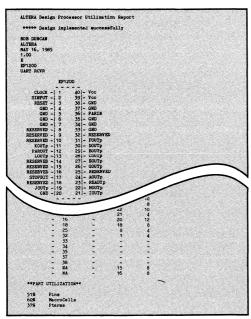

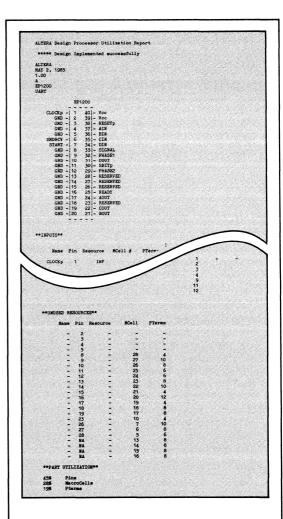

Within A+PLUS, the user may enter a design via graphic schematic diagrams, text-based netlist entries, state machine descriptions, or Boolean equations. Once the design is entered, Altera's fully automated integration process, called the Altera Design Processor (ADP), translates the design into an industry-standard (JEDEC) PLD programming file. The ADP can autonomously, or with user input, make all device pin assignments and apply sophisticated logic reduction algorithms to the design to insure optimal EPLD resource utilization. A utilization report informs the user how the design was implemented.

The JEDEC file output from the ADP can be read by Altera's LogicMap II program in order to control the programmer hardware supplied by Altera. In this way, the original designer's concept is translated into an actual EPLD device for use.

# **DESIGN ENTRY**

To begin with, the PLD user today may choose to enter his design in a number of ways affording various levels of abstraction. The trade-off in speed of entry versus microscopic design control is one the user must wrestle with.

# **BOOLEAN EQUATION ENTRY**

Boolean equations or expressions provide what some would consider the "purest" method of design entry. This method provides very quick entry for simple constructs but also assumes the user has a good grasp of his design at an equation level, which may or may not be true depending on how structured the engineer's design process is. In addition, complex structures may be difficult or cumbersome to specify at this level.

Altera's approach has been to provide Boolean equation entry capability within the overall scope of its other design entry methods. In either NetMap or schematic editor (to be described below), the user may operate in the Boolean equation domain for portions of his design, and at the gate or logic primitive level for the

remainder. Boolean entry is therefore not a strait-jacket, but another tool in the designer's repertoire.

# NETLIST CAPTURE DESIGN ENTRY

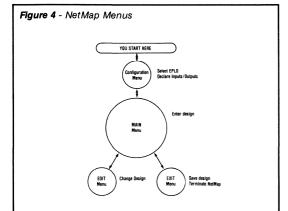

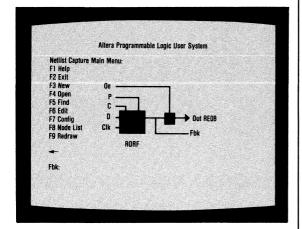

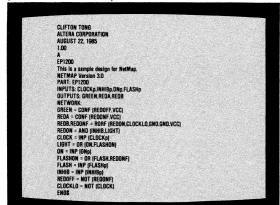

Altera's NetMap program emulates schematic capture efficiently without the need for complex graphics capability on the PC. It is well-suited to the user who has done a hand-drawn schematic or other manual design and wishes to enter it for ADP processing.

In using NetMap, the user is led through a process of selecting components and specifying interconnections by the program as he systematically traverses his design tree until all elements are specified. During the input process, NetMap makes continuous connectivity and validity checks to insure a logically correct and complete design. A pictorial display of entry progress gives the designer vivid feedback on his entry. As such, NetMap represents a very effective entry method. Boolean equation entry is also available for sections of logic within NetMap at the user's discretion. The user can operate in either or both worlds as he enters his design and has control over his level of abstraction: equation or gate.

In addition, editing of designs may be done. In this case, the NetMap module simply reads in the ADF (Altera Design File) specification of the design and prompts the user for changes.

# SCHEMATIC CAPTURE DESIGN ENTRY

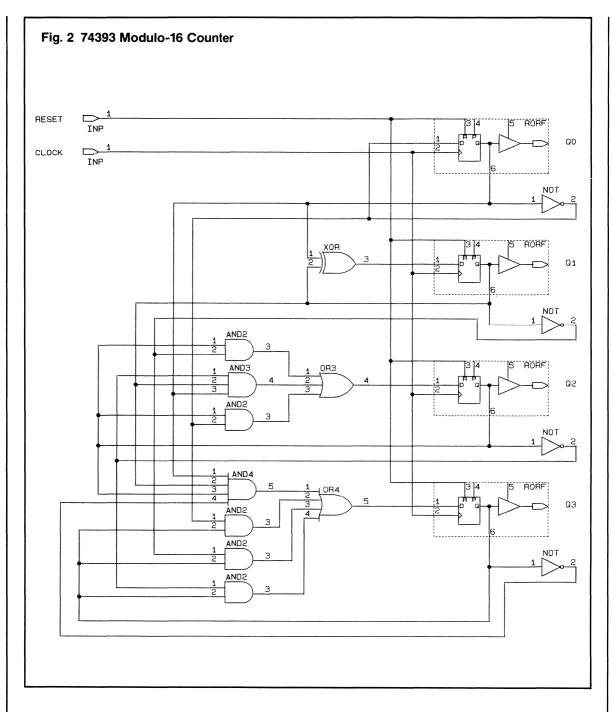

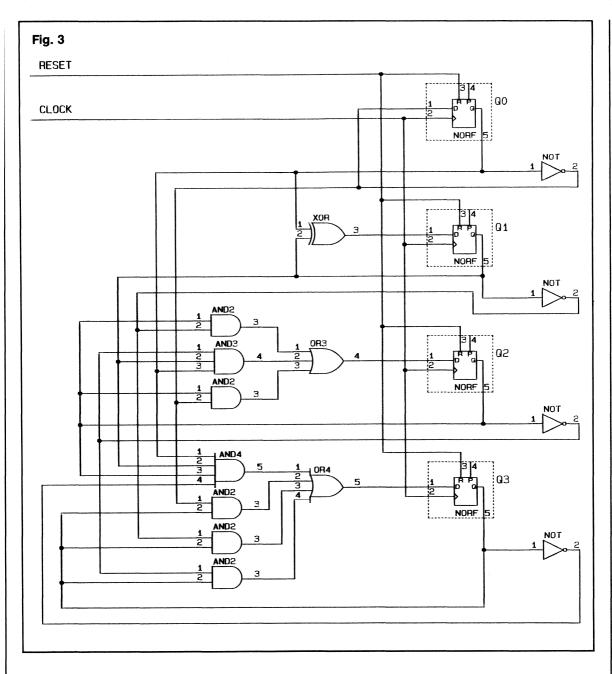

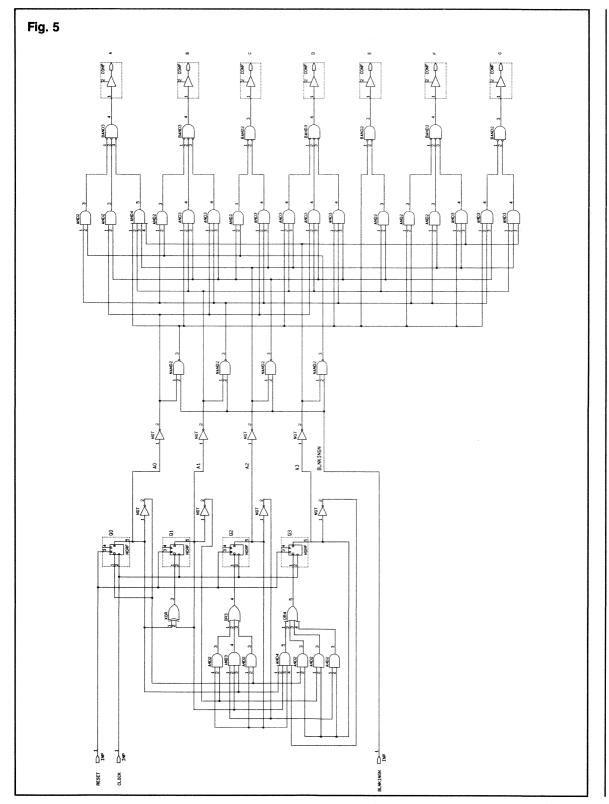

Optional graphic schematic capture packages allow the user to enter a design into the system in a user-friendly, Mouse and menu-driven environment. The design so-entered may include both schematic elements and Boolean equation elements. Schematic capture entry allows highly interactive creation and revision of a design, as well as hard copy printout of schematics on either a dot matrix, electrostatic or pen plotter.

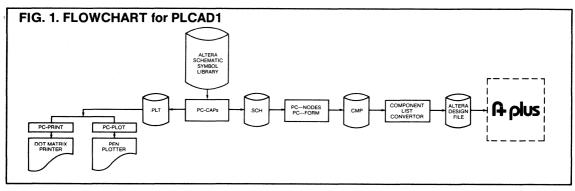

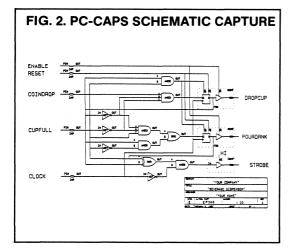

Altera supports both FutureNet's DASH-2 schematic editor, as well as P-CAD's PC-CAPS package. Both of these systems are PC-based and provide Mouse-input as mentioned previously. Menus on-screen provide a quick method to acquire system skills as well as an easy method of control on an on-going basis.

DASH-2 utilizes high-resolution graphics provided by a custom graphics adapter board and standard monochrome display. PC-CAPS provides medium-resolution color graphics through the use of a standard IBM color graphics adapter board and standard color monitor. High resolution color graphics is also optionally available.

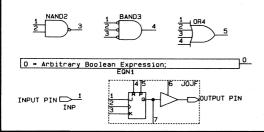

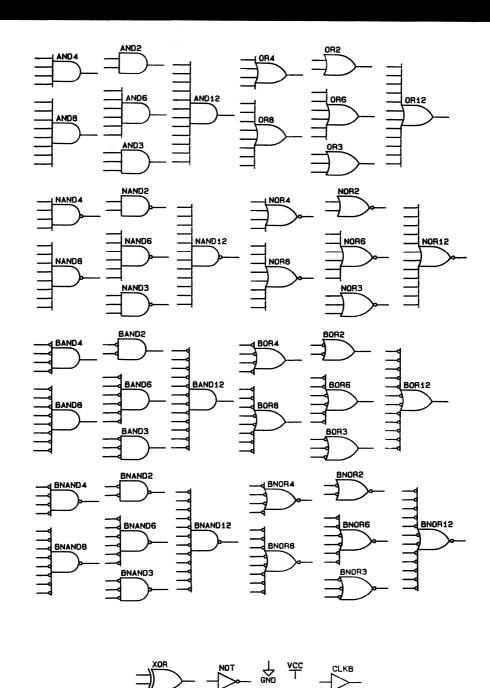

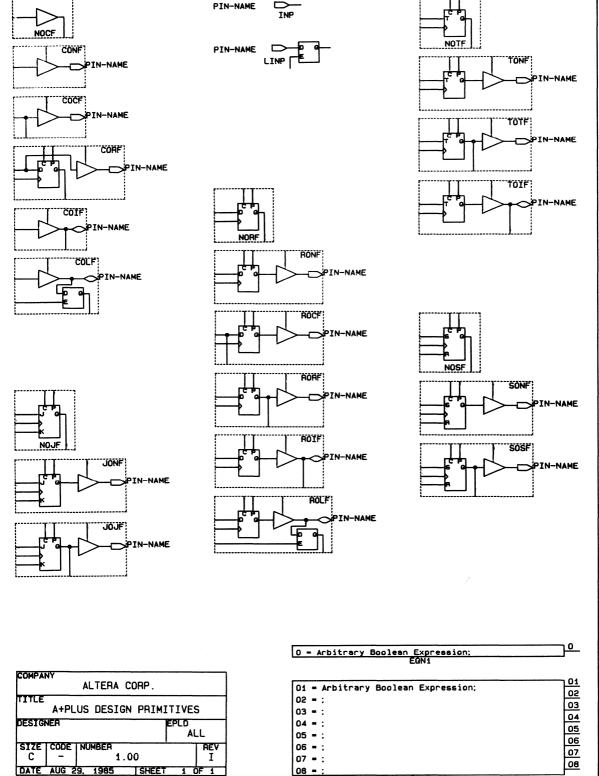

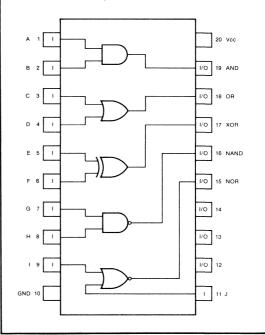

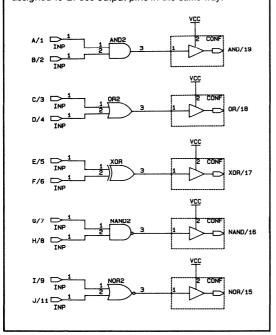

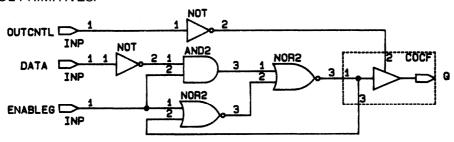

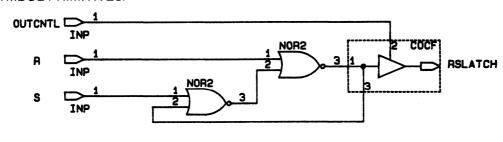

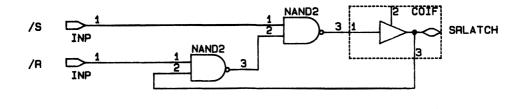

The basic functional blocks used in design entry in both systems are the Altera Design Primitives which constitute the design symbol library. An extensive set of primitives are provided for all basic logic elements such

as NAND, NOR, etc., as well as a full set of flip-flop types including D, T, JK and SR. The user can thus operate within the context of familiar TTL gate equivalents.

In addition, the user may specify a section of logic in Boolean equation form by drawing a box with the appropriate interface connections to the rest of the circuit and typing the equations defining the box's behavior into the system. The user can therefore mix entry methods as he feels appropriate.

The output of the schematic capture packages is either a pinlist or component list representing the design. These lists are then further converted into Altera Design Files (ADFs) and processed by the ADP.

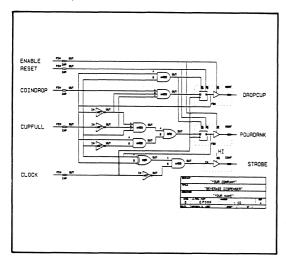

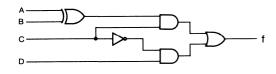

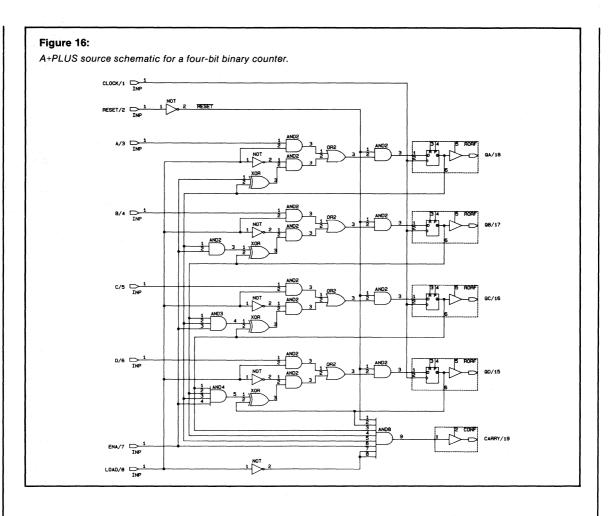

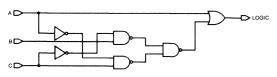

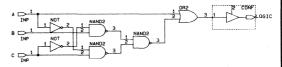

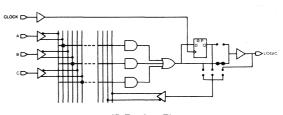

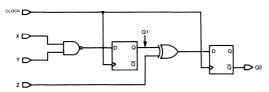

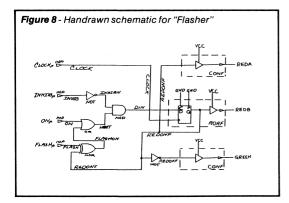

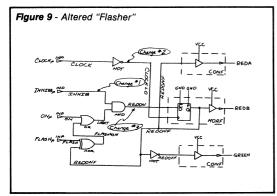

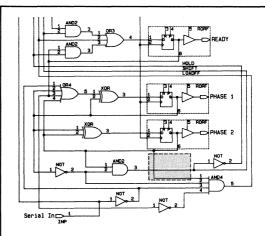

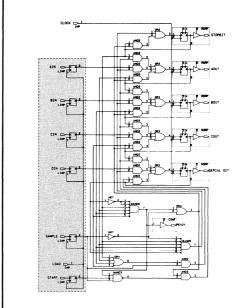

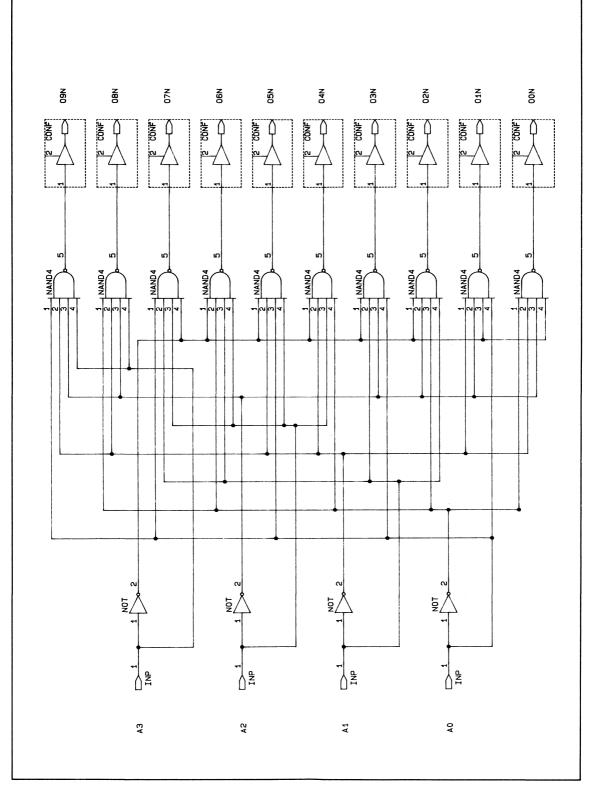

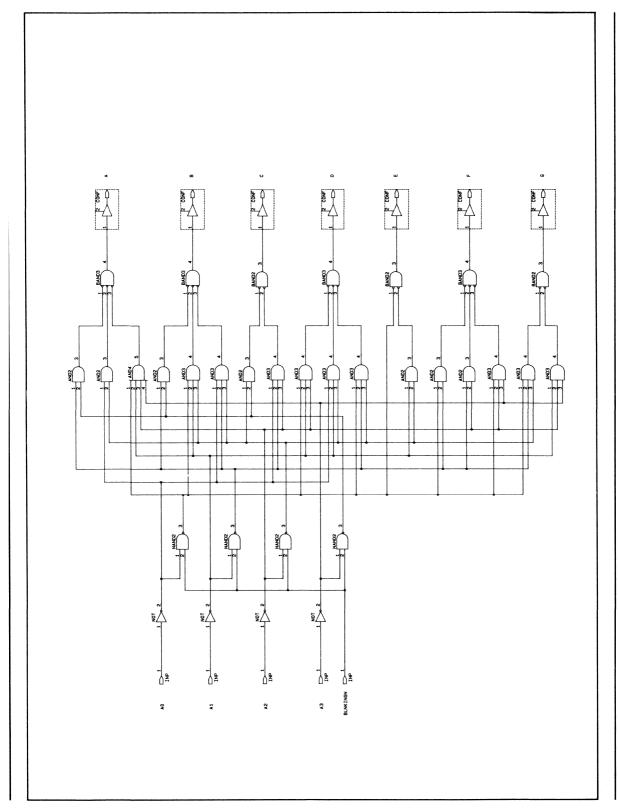

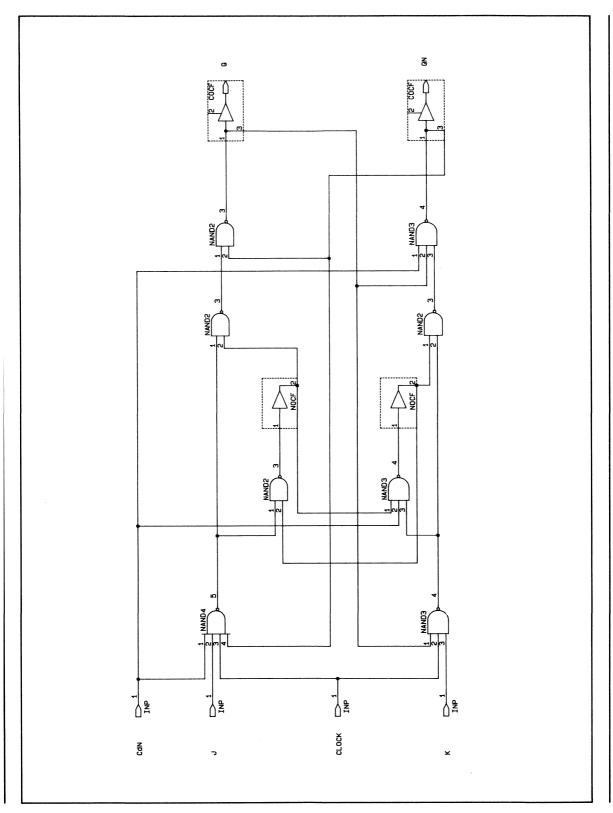

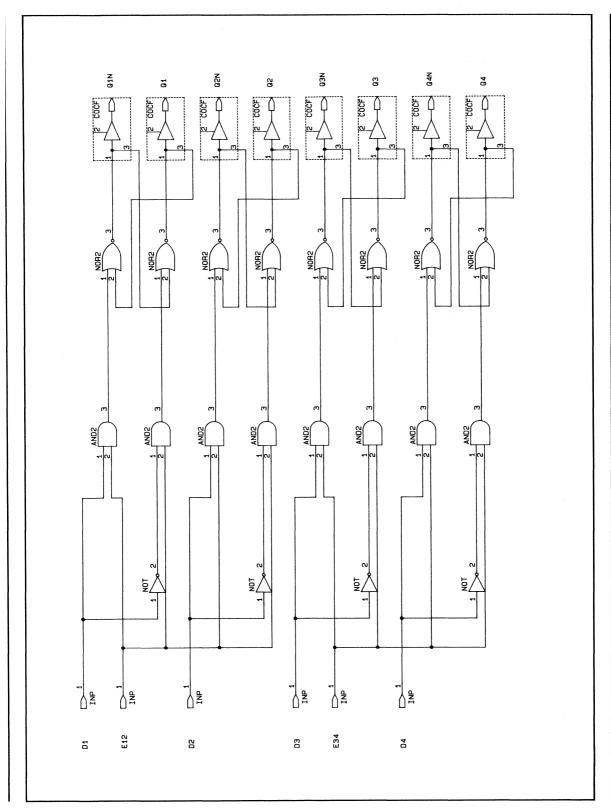

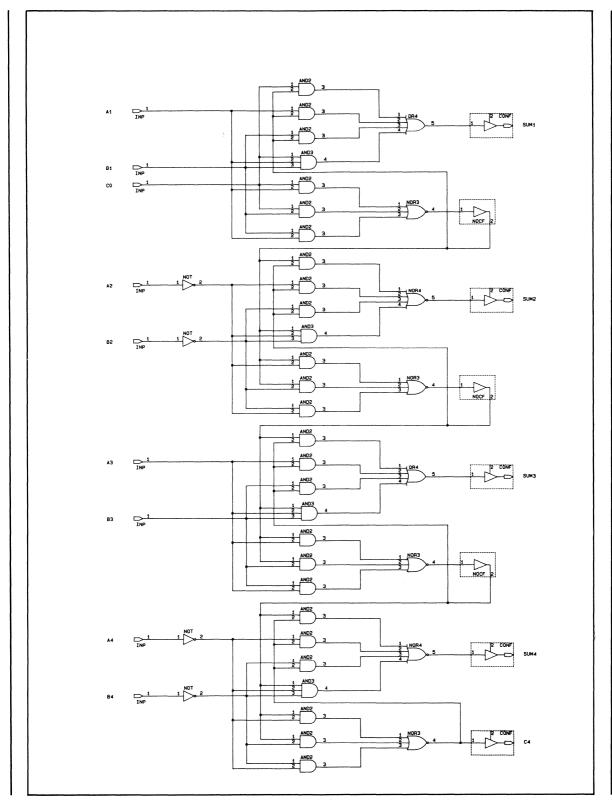

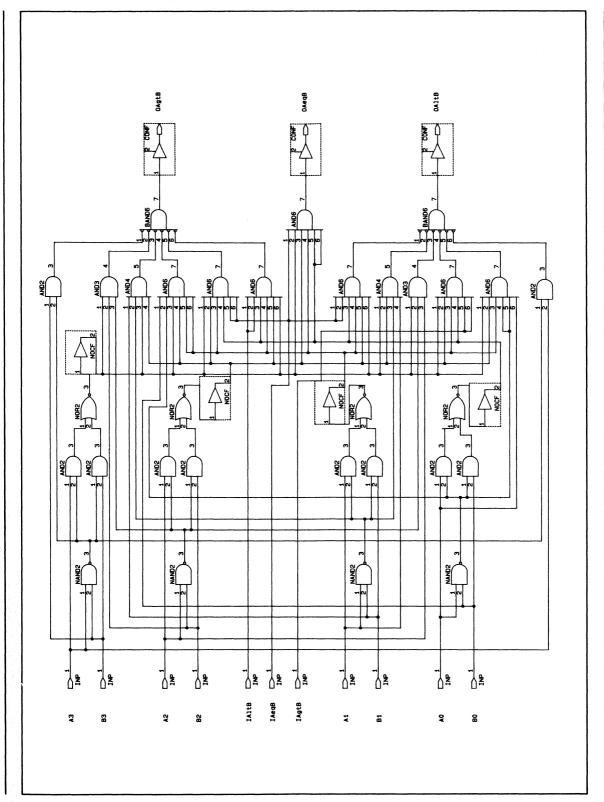

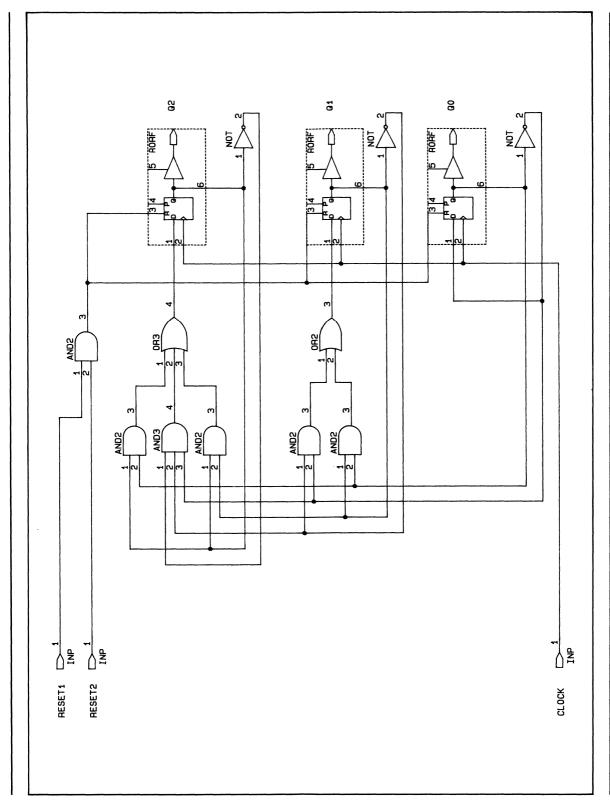

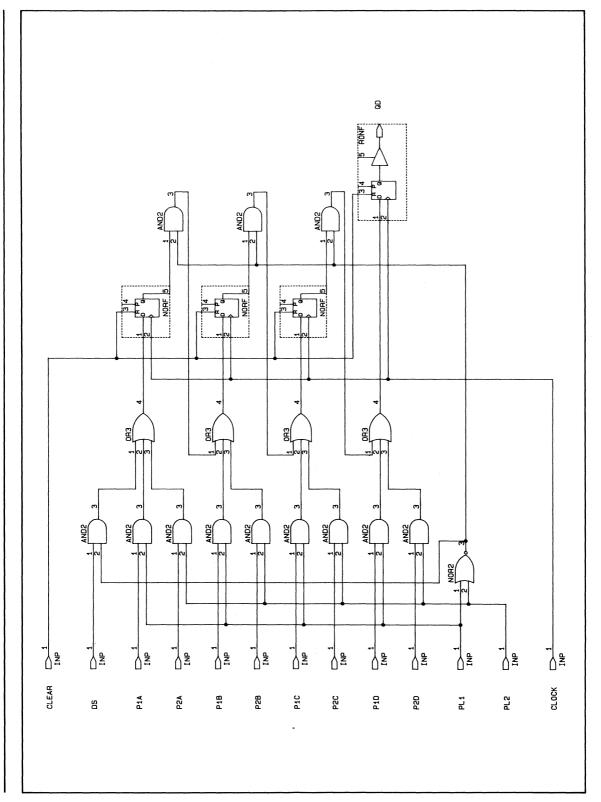

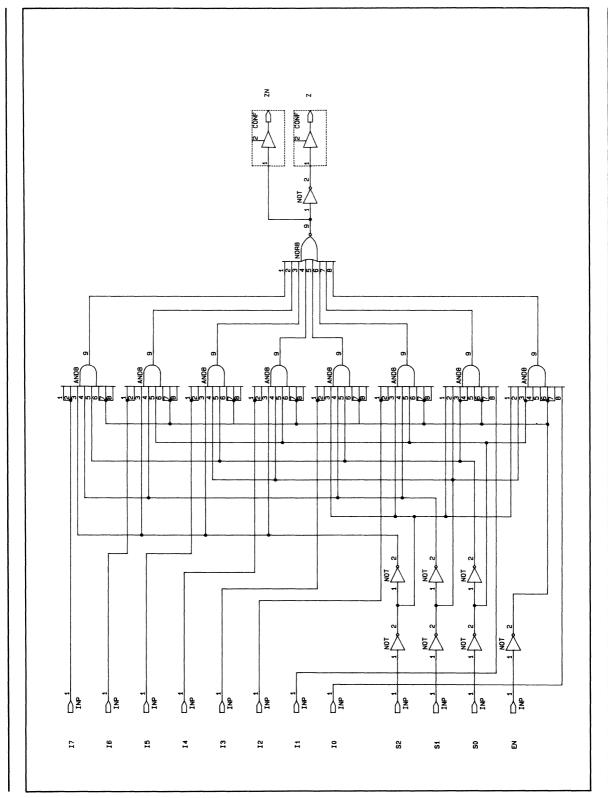

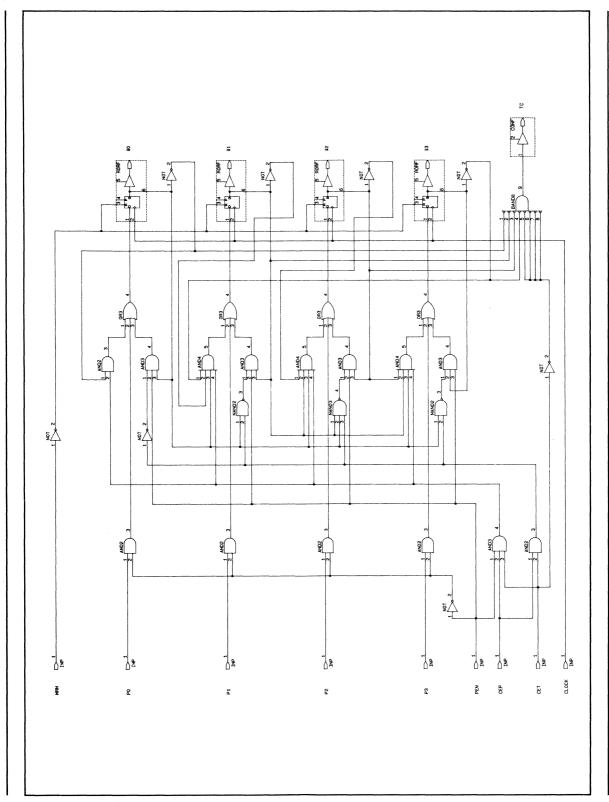

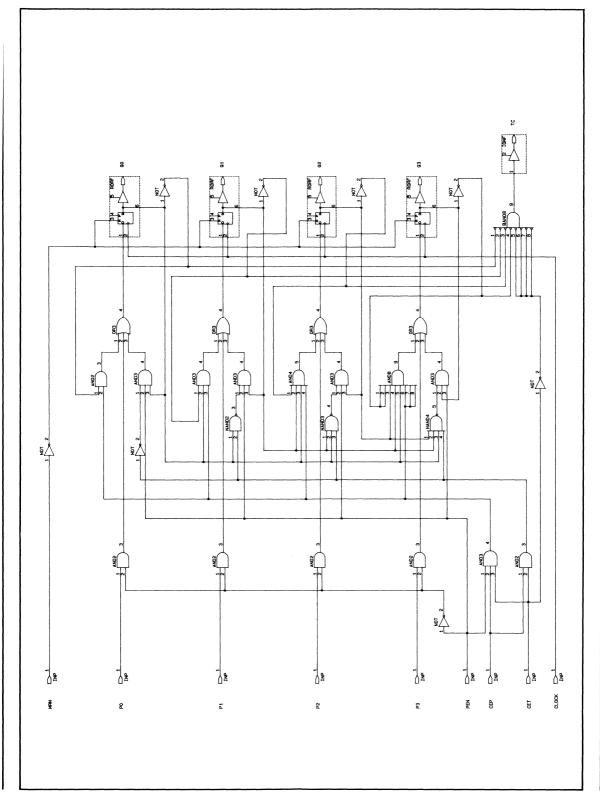

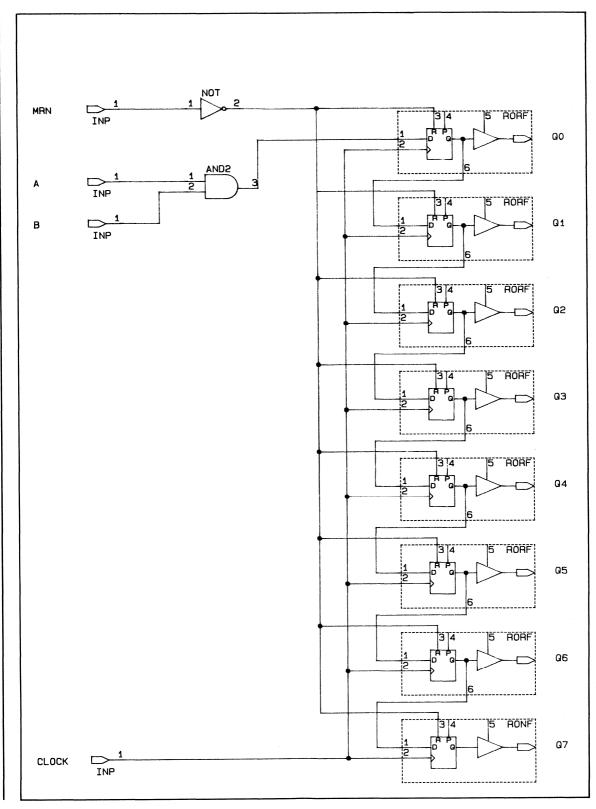

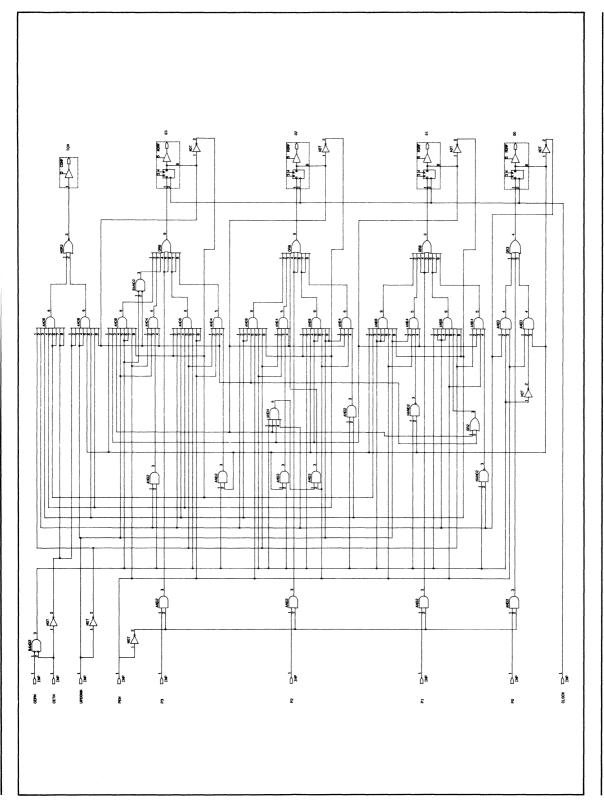

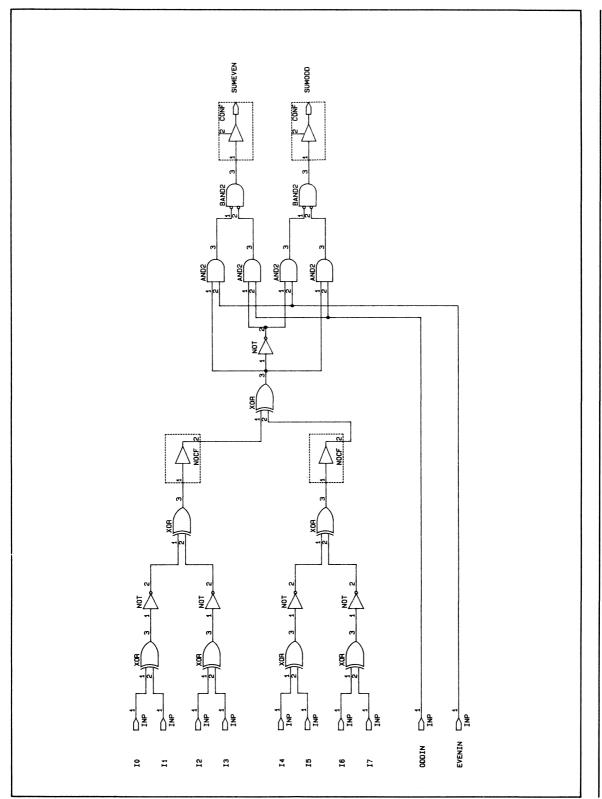

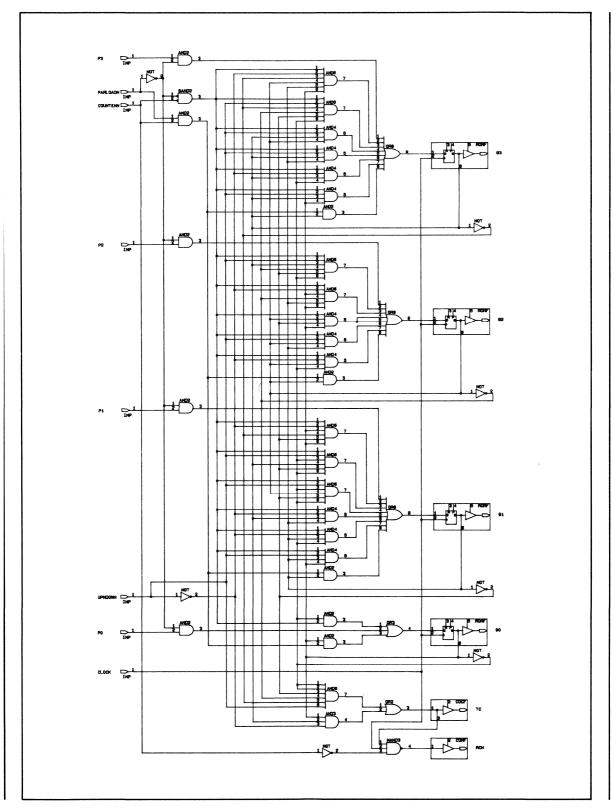

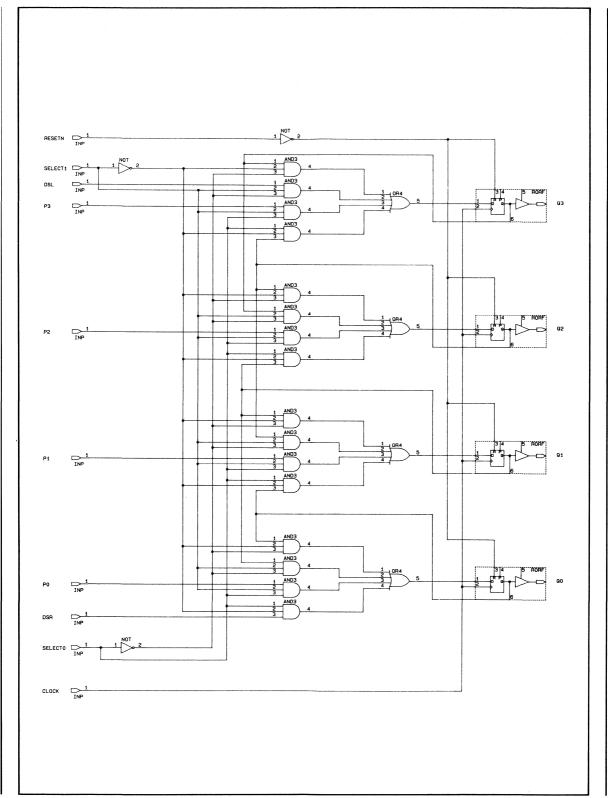

A sample schematic is shown below.

# STATE MACHINE DESIGN ENTRY

State Machine entry provides the user the most abstract and highest level method of specifying his design. As such, it tends to be an efficient entry method but one which tends to insulate the user (for better or worse) from the gate-level logic. A+PLUS provides several methods for specifying designs as state machines. In all cases, the resulting designs are automatically processed by the ADP including logic minimization.

The user can specify states and conditional branches, as well as specify inputs and outputs to the state machines.

State machine descriptions may also be input directly into the Design File in the form of state tables. This allows the user to specify a state machine in terms of inputs, outputs and state transitions in tabular form.

In summary, the user has a variety of formats to work from. Compatibility with existing methodologies, speed of entry, and accuracy of representation are

considerations which will determine ultimately how the user performs this front-end task.

## **FITTING**

The translation of a design from its original input format (be it equation, schematic, or other) to a device-specific programming map is typically called fitting. Early PAL assemblers provided no support for software-assisted logic minimization: the user in essence had to determine the minimal set of equations to implement his logic. This could be quite time consuming and was early-on recognized as a mechanical task well suited to software algorithms.

Altera's ADP package utilizes logic minimization schemes such as DeMorgan's Inversion to aid the designer in minimizing his logic and optimally fitting into a given device. This process becomes more complex as devices become more sophisticated. Variable product term distribution, multiple flip-flop types, local / global feedback all complicate the process as they add capability.

Fitting is a process which is obviously sensitive to device architecture. A very compelling reason for vendor-supplied development tools such as Altera's A+PLUS is the need for close interaction between tools and architecture. Much as optimizing compilers must have knowledge of the target computer architecture, fitters must have knowledge of their devices. Tools developed in parallel with device development will arrive in a timely fashion at device introduction rather than lagging by substantial periods of time.

Altera's answer to the fitting problem is its ADP package. It performs three major functions.

First, regardless of the type of design entry method used, it translates the design into internal logic equations. At this stage, most design syntax errors are detected and reported to the user.

Second, the ADP perfoms sophisticated Boolean logic reductions on the translated design in order to maximize utilization of the EPLD's resources. The user is given complete control over the application of minimization and inversion techniques.

Finally, the ADP matches requirements of a specific design with the known resources of an Altera part. The actual fitting process results in a utilization report and a JEDEC standard programming file. The JEDEC file is used to directly program the target EPLD using Altera-supplied hardware, or general-purpose third party programmers.

In essence, the fitter is where the design and PLD meet. As such, close coupling is required. General-purpose tools are often found lacking or very late in addressing this essential step.

# **PROGRAMMING**

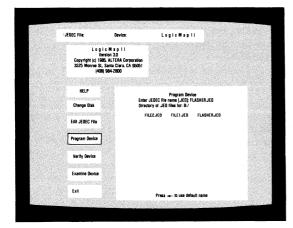

The LogicMap II program provides a graphical

user interface between the JEDEC Standard File output by the ADP and the Altera Logic Programmer hardware.

LogicMap II allows a user to edit a JEDEC Standard File and controls programming of the target Altera EPLD based upon it. In addition, it can read the contents of a programmed part (if the Security Bit is not set) to allow program verification. This capability also allows generating a JEDEC file from a previously programmed device for easy pattern duplication.

During the editing of JEDEC files, LogicMap II operates in a hierarchy of four levels. Information is displayed through a series of easy-to-use windows. The levels range from a local, detailed view of the device program, to a global block view. The combination allows rapid scoping in and out of the user's view.

LogicMap II provides an easy to use interface to the Altera Logic Programmer hardware. LogicMap II also provides control over two special features available in Altera EPLDs: the Verify Protect feature, implemented via the so-called Security Bit which prevents the part from being interrogated or inadvertently programmed, and the Turbo-Bit which allows the user to trade-off speed and power characteristics of a part.

In summary, LogicMap II provides a smooth interface between programming file and device. Altera's emphasis on maximum designer productivity carries through to this last part of the design implementation.

# **SIMULATION**

Design checking before system integration from components has taken on new importance with more complex designs. Granted, with EPLDs the user does have the luxury of relatively painlessly reprogramming his device if an error in the design should be found. However, by employing simulation at an early stage this type of wasted effort can be prevented.

Logic simulation, until relatively recently, has been relegated to large, complex programs running on mainframe computers. Simulation now is available on PCs, such as PCAD's PC-LOGS.

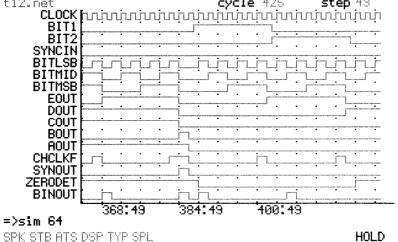

PC-LOGS is a program which allows the user to model the behavior of a circuit designed with Altera's Design Primitives and the PC-CAPS editor. The simulation program provides either graphical or tabular display of the response of the circuit to a user-supplied input pattern. The user can observe the design's response before committing it to hardware.

PC-LOGS is an interactive, event-driven, 12 state simulator. Being event driven, the program keeps track of and updates circuit node states only upon a node changing state. This method considerably shortens simulation time as opposed to blindly evaluating all nodes every time an event occurs. Input stimulus to the circuit can also be easily supplied in a variety of formats. Fault injection (stuck-at-zero, stuck-at-one) is also supported.

PC-LOGS requires no additional hardware beyond the PC to run. As a result, it is a very cost-effective arrangement.

# **TEST CONSIDERATIONS**

As in the simulation arena, the problem of testing FPLDs is in some sense a subset of system test issues. Concerns at the system level are likely to be mirrored at the FPLD component level.

It must be mentioned that FPLD technologies do have an impact on the need for application-specific test generation. By nature of bipolar fuse technology and the fact that these devices are not reprogrammable, the manufacturer cannot by definition test every logic element before shipment. As such, programming yield is less than 100% and may typically be in the 90% range. Erasable technologies, however, allow the programming and erasure of all elements, and thus the devices are generically testable. The manufacturer can thus guarantee essentially 100% programming yield for the customer.

Besides the obvious savings in paid-for but unshippable components, the user of a generically testable device has substantially reduced his concern with respect to hidden faults residing in the final device due to an improperly blown fuse. Remaining "holes" in the fault coverage of final test programs are more easily conscienced when the individual component has been exhaustively checked.

Aside from the above concerns, PLDs hold no special problems for the user during test. Reliablity of the programming elements has proven good for all technologies. The user is not likely to modify the method of or extent of his final system test due to the inclusion of PLDs.

## CONCLUSION

Existing EPLDs provide a flexible level of integration positioned above traditional TTL and below high-end gate arrays and LSI devices. The emphasis on rapid design turnaround will drive system designers more and more toward the flexibility of EPLD devices.

Future EPLD devices will incorporate new architectures which will allow the rapid design of complex devices with the equivalent of several thousand gates on a single chip. The result will be the integration of complex subsystems on single chips much as large-scale gate arrays permit today.

Portions of the design process such as schematic entry are best left to general-purpose tools supplied by third parties. Tool selection in these areas is based upon global user design concerns, not specific PLD issues. In the areas of fitting and programming, however, PLD device-specific tools are needed, and these must be provided early in the device life at introduction. Altera is committed to supplying this capability.

# **DATA SHEETS**

# PAGE NO.

| Nicona di al I latino di Bondo de | 40   |

|-----------------------------------|------|

| Numerical Listing of Products     | . 10 |

| Product Selection Guide           | . 19 |

| EP300/EP310                       | . 20 |

| EP600                             | . 29 |

| EP1200/1210                       | . 41 |

| EP900                             | . 53 |

| EP1800                            | . 65 |

| PLDS2, PLE4, PLE5                 | . 67 |

| PLS2                              | . 70 |

| PLCAD1, PLE1, PLE2                | . 73 |

| PLCAD2, PLE10, PLE20              | . 75 |

| PLSIM1                            | . 77 |

| PLDSMA1, PLDSMA2, PLDSMA3         | . 79 |

| A+DESIGN PRIMITIVES               | 80   |

# **PRODUCT LISTING**

| PRODUC             | T                                       | PAGE NO                               |

|--------------------|-----------------------------------------|---------------------------------------|

| EP300              | DC                                      | 20                                    |

| EP300              | DM                                      | 20                                    |

| EP300-2            | DC                                      | 20                                    |

| EP310              | DC                                      | 20                                    |

| EP310              | DM                                      | 20                                    |

| EP310-2            | DC                                      |                                       |

| EP310-1            | DC                                      |                                       |

| EP600              | DC                                      |                                       |

| EP600              | JC                                      |                                       |

| EP600              | DM                                      |                                       |

| EP600              | JM                                      |                                       |

| EP600-3            | DC                                      |                                       |

| EP600-3            | JC                                      |                                       |

| EP600-2            | DC                                      |                                       |

| EP600-2<br>EP600-1 | JC                                      |                                       |

| EP600-1            |                                         |                                       |

| EP900-1            |                                         |                                       |

| EP900<br>EP900     |                                         |                                       |

| EP900              | JC                                      |                                       |

| EP900-2            | JM<br>DC                                |                                       |

| EP900-2            | JC                                      |                                       |

| EP900-1            | DC                                      |                                       |

| EP900-1            | JC                                      |                                       |

| EP1200             | DC                                      |                                       |

| EP1200             | JC                                      |                                       |

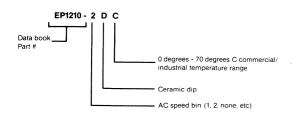

| EP1210             | DC                                      |                                       |

| EP1210             | JC                                      |                                       |

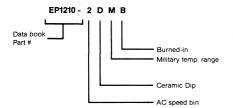

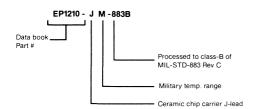

| EP1210             | JM                                      |                                       |

| EP1210-2           | DC                                      |                                       |

| EP1210-2           | JC                                      | 41                                    |

| EP1210-1           | DC                                      |                                       |

| EP1210-1           | JC                                      | 41                                    |

| EP1800             | JC                                      |                                       |

| EP1800             | JM                                      | 65                                    |

| PLDS2              |                                         | 67                                    |

| PLE4               |                                         |                                       |

| PLE5               |                                         |                                       |

| PLS2               |                                         |                                       |

| PLCAD1             | *************************************** |                                       |

| PLE1               |                                         |                                       |

| PLE2               |                                         |                                       |

| PLCAD2             | *************************************** | · · · · · · · · · · · · · · · · · · · |

| PLE10              | *************************************** |                                       |

| PLE20              |                                         |                                       |

| PLSIM1             |                                         | 77                                    |

| PLDSMA1            |                                         |                                       |

| PLDSMA2            |                                         | 79                                    |

| PLDSMA3            |                                         |                                       |

| A+DESIGN           | N PRIMITIVES                            | 80                                    |

# PRODUCT SELECTION GUIDE

|                               |       |       | PR    | ODUCT T | YPE    |        | And the state of t |  |  |  |  |  |  |  |

|-------------------------------|-------|-------|-------|---------|--------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| QUANTITATIVE DATA             | EP300 | EP310 | EP600 | EP900   | EP1200 | EP1210 | EP1800                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |

| Pins                          | 20    | 20    | 24    | 40      | 40     | 40     | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Inputs                        | 18    | 18    | 20    | 38      | 36     | 36     | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Outputs                       | 8     | 8     | 16    | 24      | 24     | 24     | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Macrocells                    | 8     | 8     | 16    | 24      | 28     | 28     | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Product Terms                 | 74    | 74    | 160   | 240     | 236    | 236    | 480                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| ¹Equivalent Gates             | 352   | 352   | 716   | 1096    | 1176   | 1176   | 2140                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| Standby Current (mA@5v)       | 25    | 20    | .01   | .01     | 3      | 3      | .01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Active Current (mA@5v, 10MHz) | 25    | 20    | 15    | 30      | 35     | 25     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Max Clock Speed (MHz)         | 18.2  | 40    | 40    | 33.3    | 12     | 20     | 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

# **FEATURES** Input Latches Programmable I/O **TRI State Outputs Programmable Output Polarity Programmable Registers Buried Registers** Register By-pass Register Pre Load Register Reset Programmable Clock Synchronous Clocking **Asynchronous Clocking Product Term Sharing** Variable Product Term Dist Global-Local Busing Security Bit Erasable (U.V.) Ceramic Dip Package

Ceramic J Lead Package

<sup>&</sup>lt;sup>1</sup>See AB12, Page 225

€P300 €P310

# EPLD ERASABLE PROGRAMMABLE LOGIC DEVICE

# **FEATURES**

- Programmable replacement for conventional fixed logic.

- EPROM technology allows reprogrammability, ensures high programming yield and ease of use.

- Second generation programmable logic architecture allows up to 18 inputs and 8 outputs.

- Each output is User Programmable for combinatorial or registered operation, in active high or low mode.

- Each output also has an independently *User Programmable* feedback path.

- 100% generically testable—provides 100% programming yield.

- Programmable "Security Bit" allows total protection of proprietary designs.

- Advanced software support featuring Schematic Capture, Interactive Netlist, Boolean Equation and State Machine design entry.

- Advanced CHMOS II-E circuitry for systems requiring low power, high performance speeds, and immunity to noise (EP310).

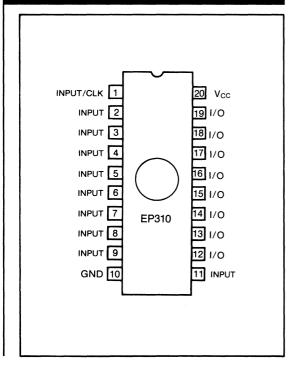

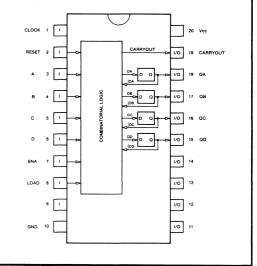

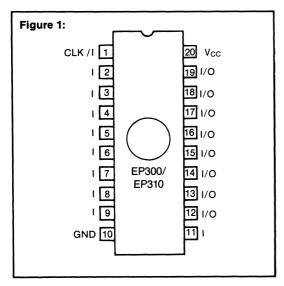

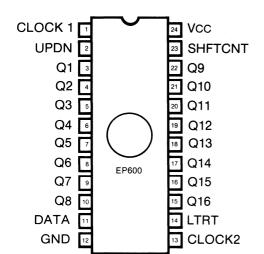

## **CONNECTION DIAGRAM**

# **GENERAL DESCRIPTION**

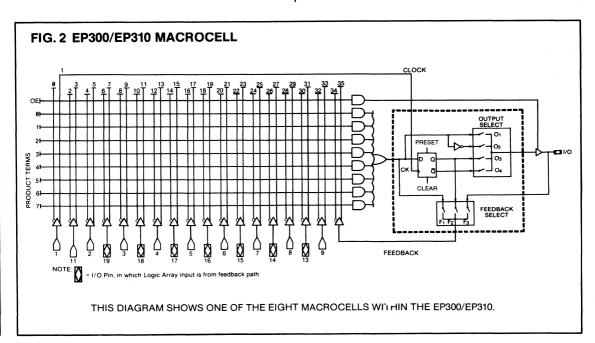

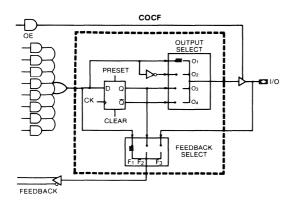

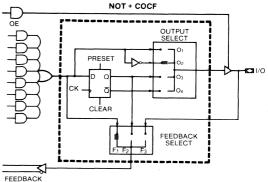

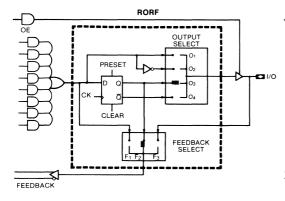

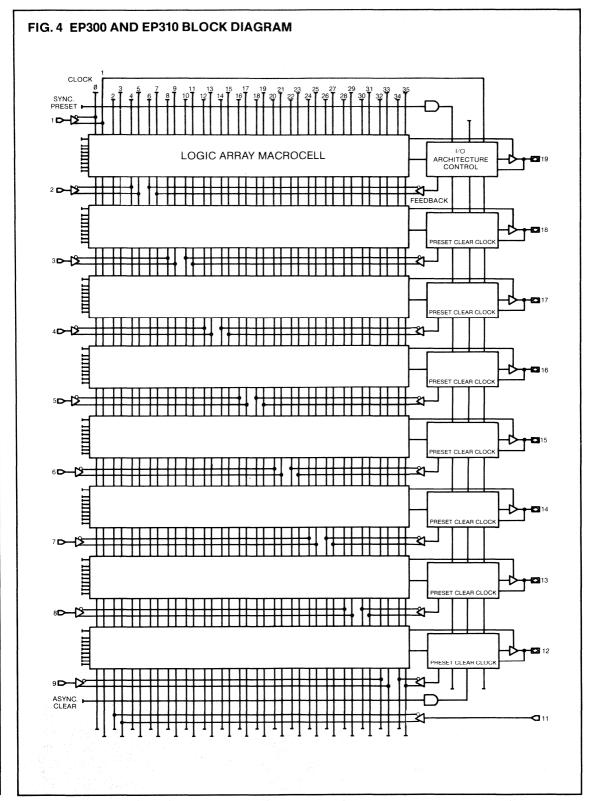

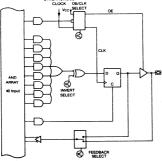

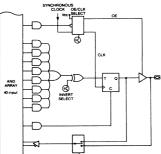

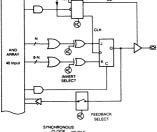

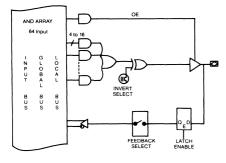

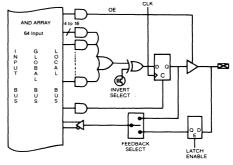

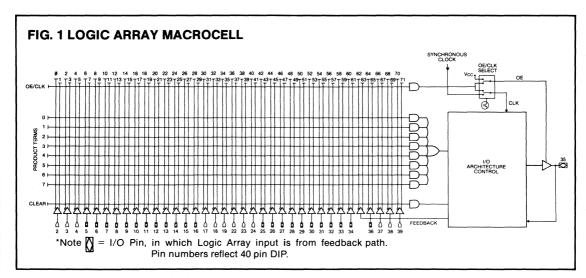

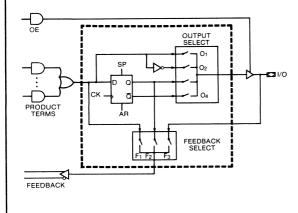

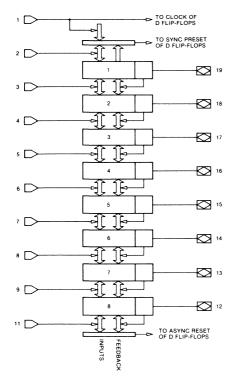

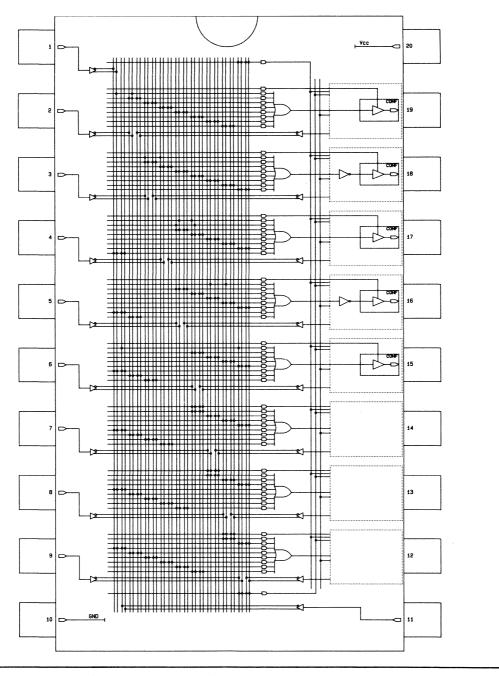

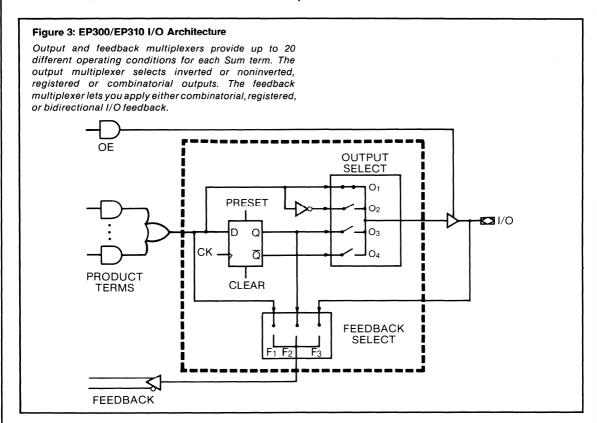

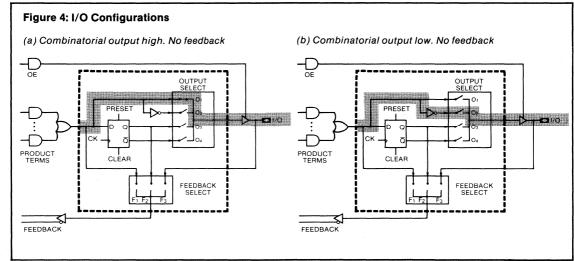

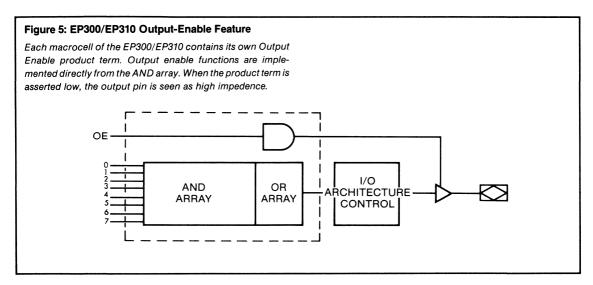

The ALTERA EP300/EP310 combine the power, flexibility, and density advantages of CMOS, EPROM technology with second generation programmable logic array architecture. This combination defines a new capability in electrically programmable logic. The EP300/EP310 utilizes the familiar sum-of-products architecture which allows users to program complex custom logic functions quickly and easily. Up to 18 inputs and 8 outputs are provided, with eight product terms and a separate Output Enable term for each output.

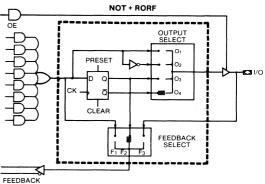

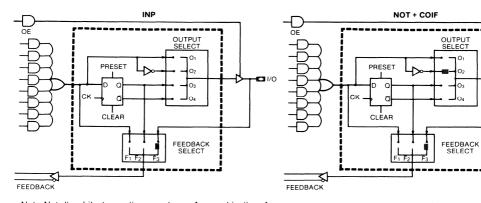

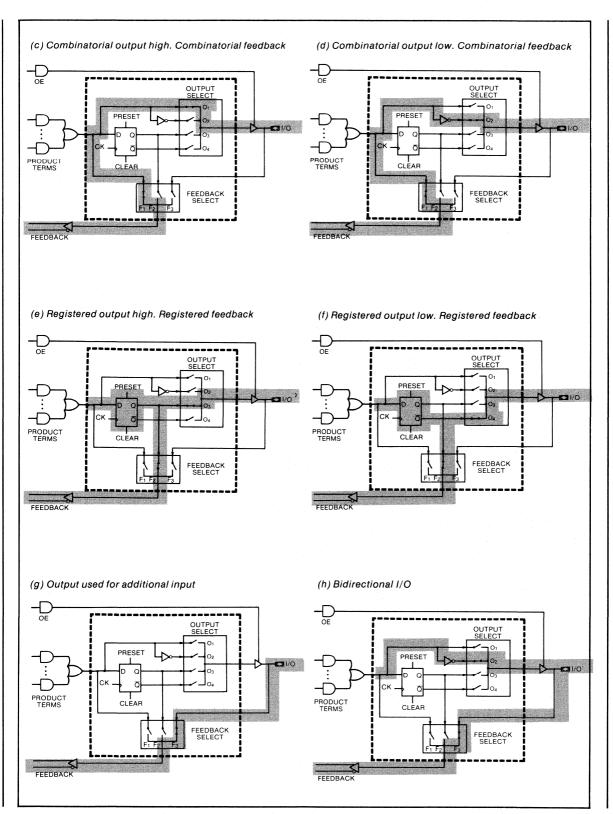

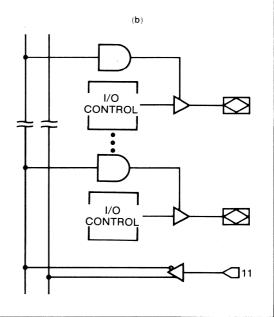

A unique feature of the EP300/EP310 is the ability to program each output architecture on an individual basis. This gives the user the flexibility to assign either combinatorial or registered output, in either active high or active low mode, to each output pin. In addition, the feedback path can be programmed independently of the output to be either combinatorial, registered, or I/O. Other advantages include: 100% generic testing (all devices are 100% tested at the factory). The device can be erased with ultraviolet light. Design changes are no longer costly, nor is there a need for post programming testing.

Programming the EP300/EP310 is accomplished with the use of Altera's A+PLUS development software which supports four different design entry methods. Once the circuit has been entered, the A+PLUS software performs automatic translation into logical equations, boolean minimization, and design fitting directly into an EP300/EP310.

**REV 4.0**

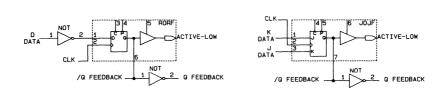

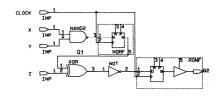

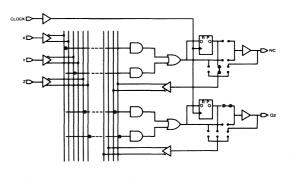

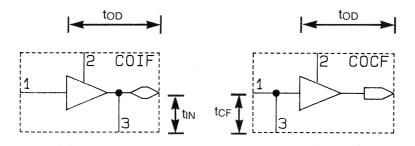

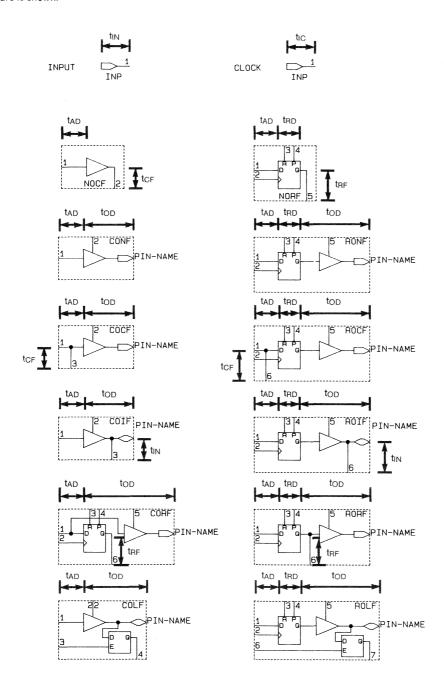

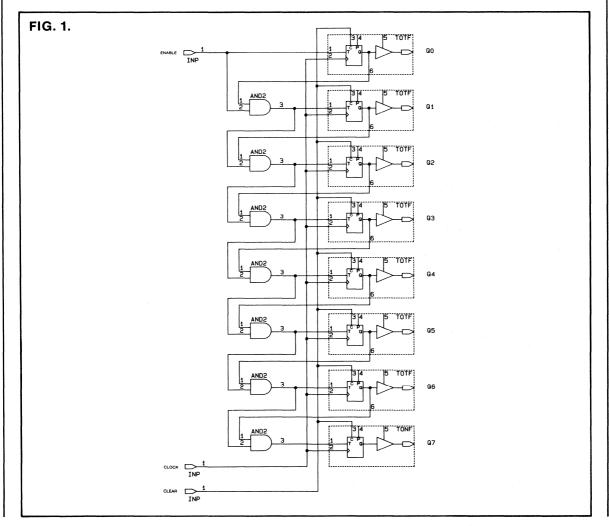

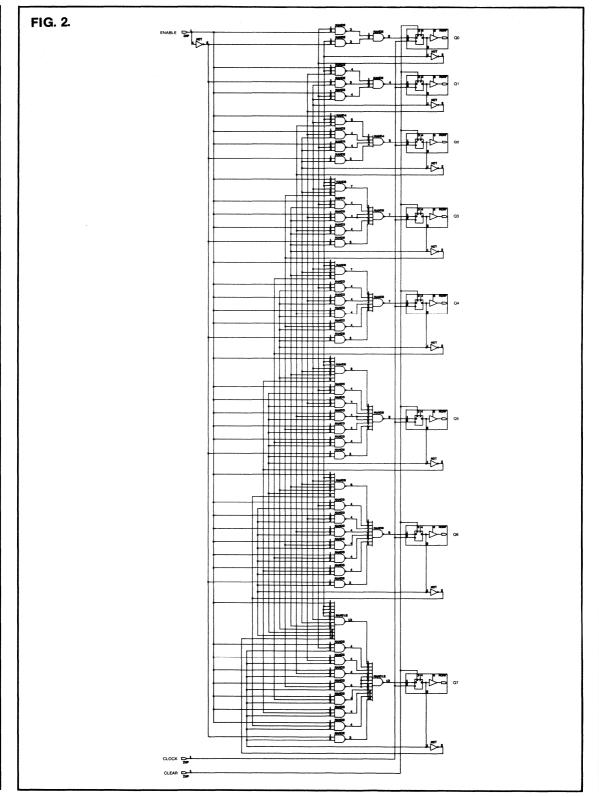

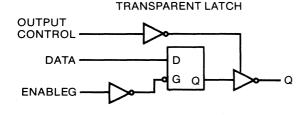

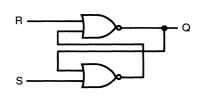

# **FUNCTIONAL DESCRIPTION**

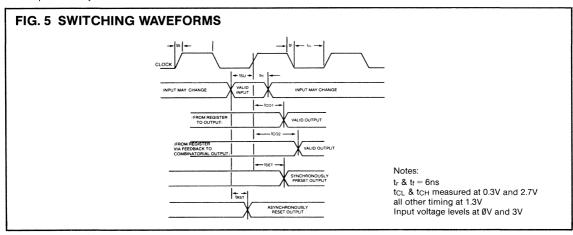

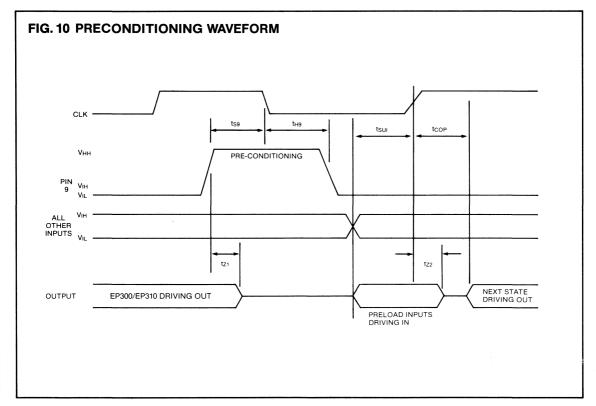

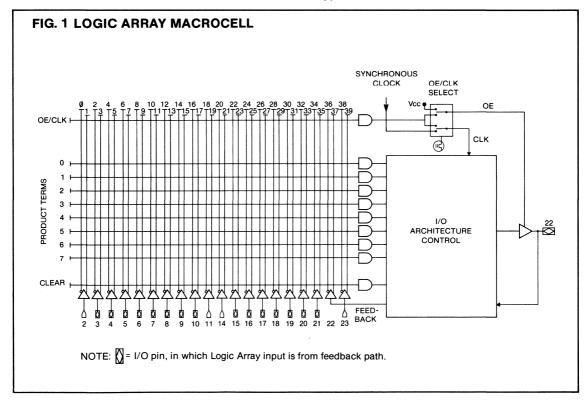

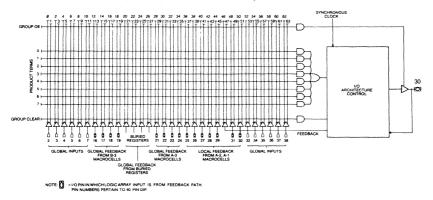

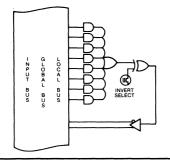

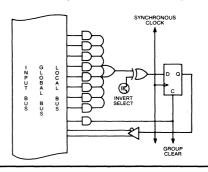

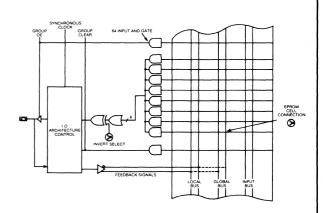

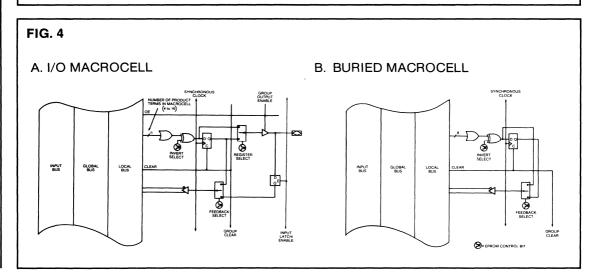

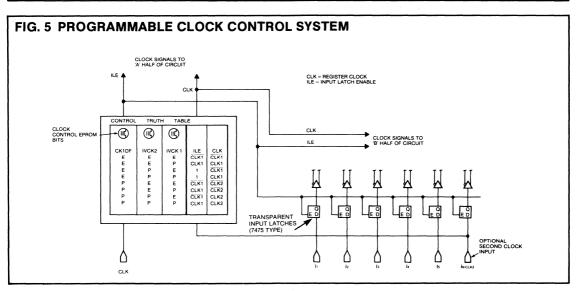

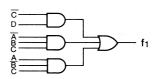

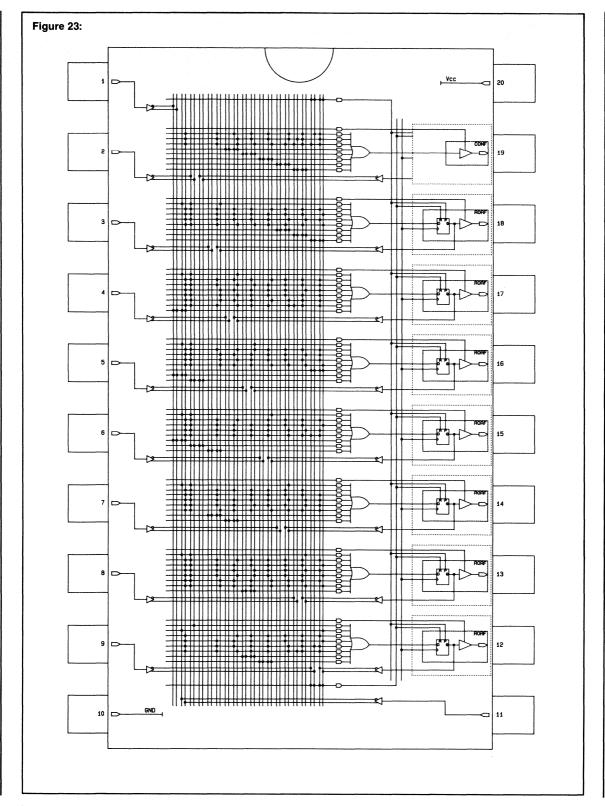

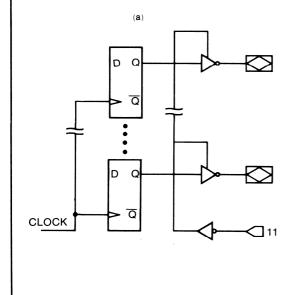

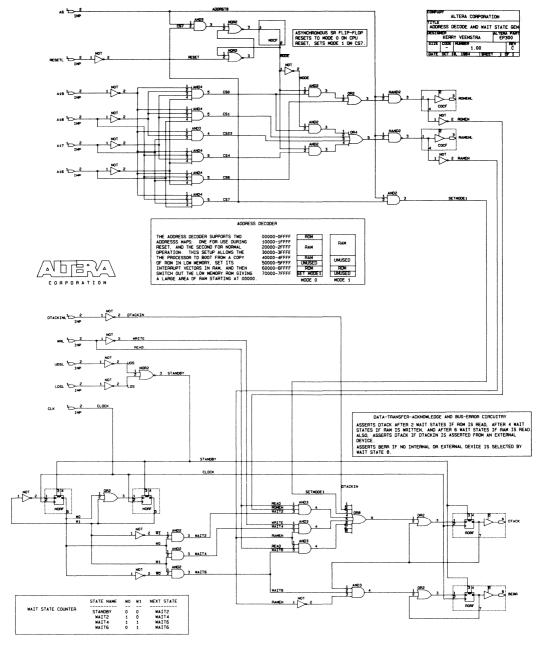

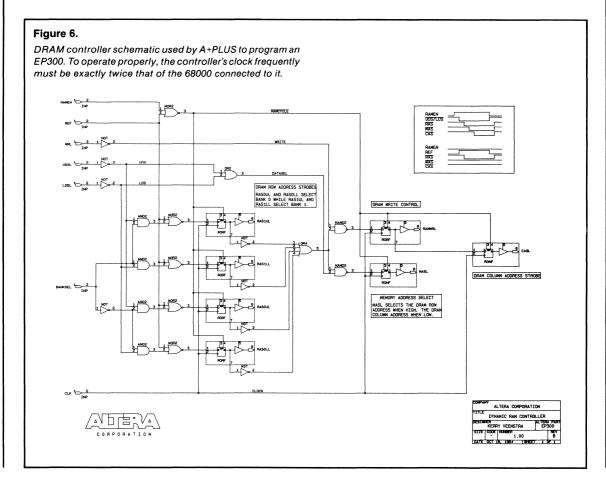

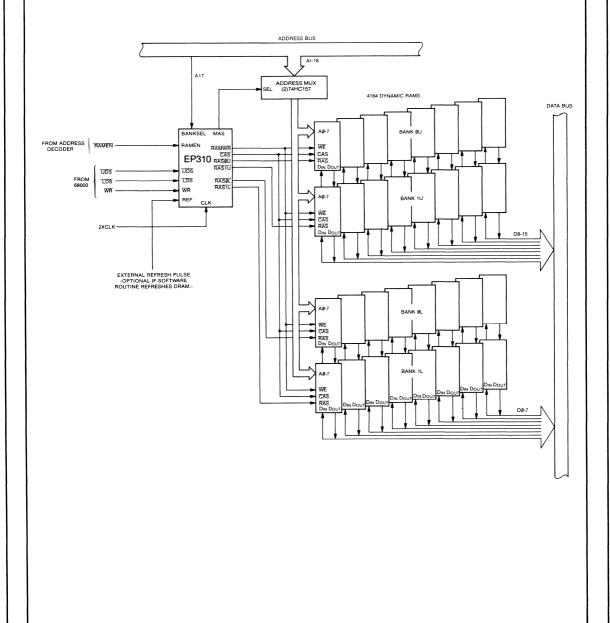

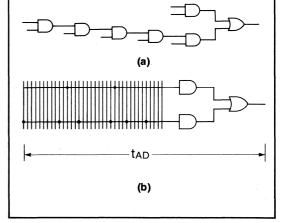

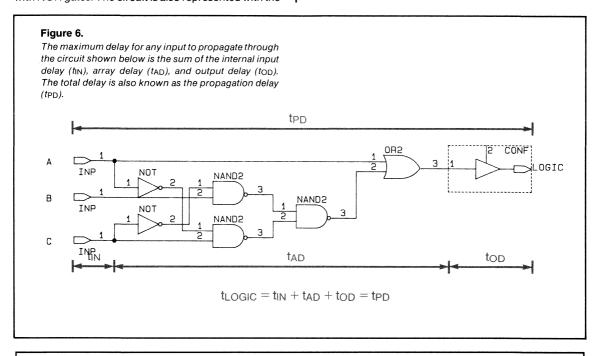

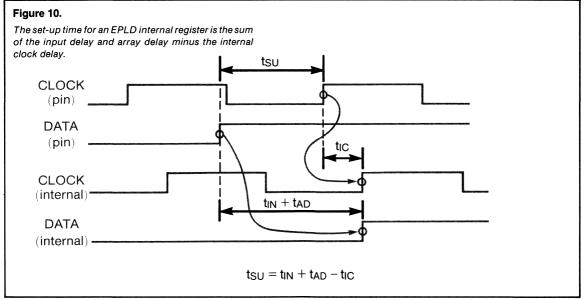

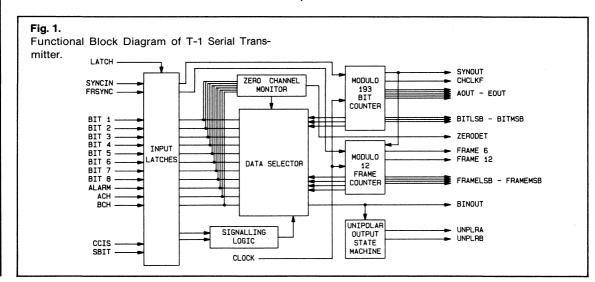

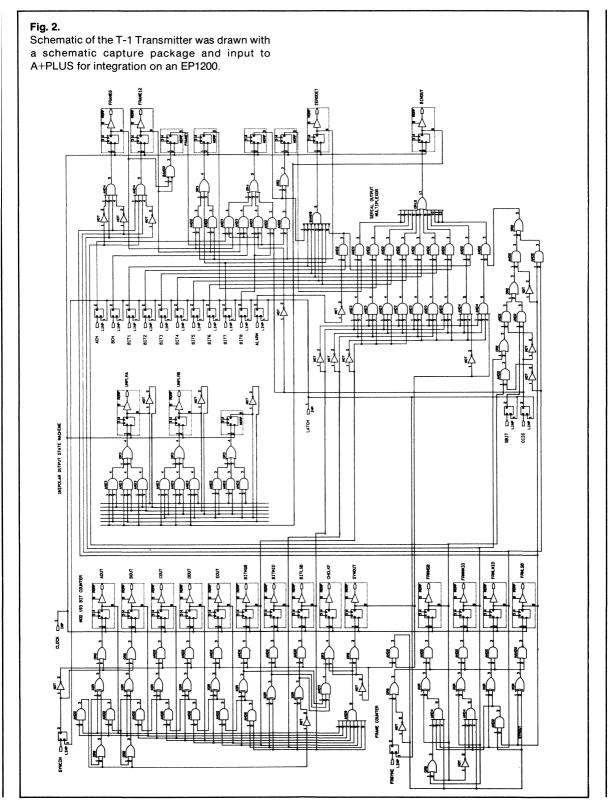

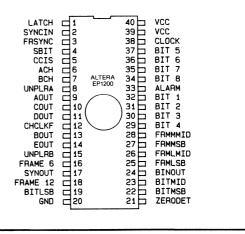

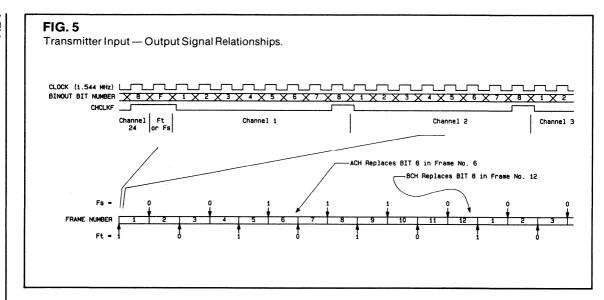

A block diagram of the EP300/EP310, along with logic diagrams of the I/O Architecture Control function and the Logic Array Macrocell are shown in figures 2 through 4. The EP300/EP310 is organized in the familiar sum-of-products format with a total of 74 product terms and 36 input lines.